いまいちはっきりしない

Core Complexの構造

昨年開催されたAMDの発表会Next Horizonでも、今年のCESの基調講演でもはっきりしなかったのはCCXの構造である。

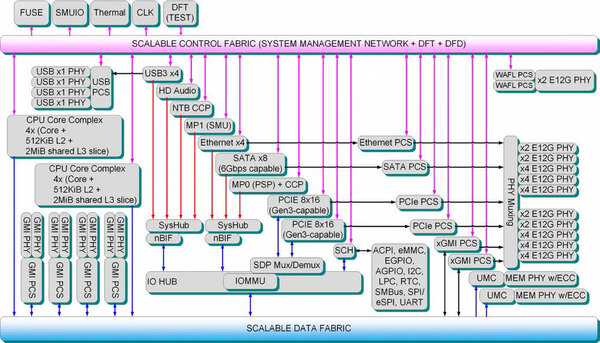

下の画像はZenベースのダイの内部ブロック図であるが、2つのCCXは直接つながっておらず、インフィニティ・ファブリック経由での接続となる。

画像の出典は、“Processor Programming Reference (PPR) for AMD Family 17h Model 01h, Revision B1 Processors”

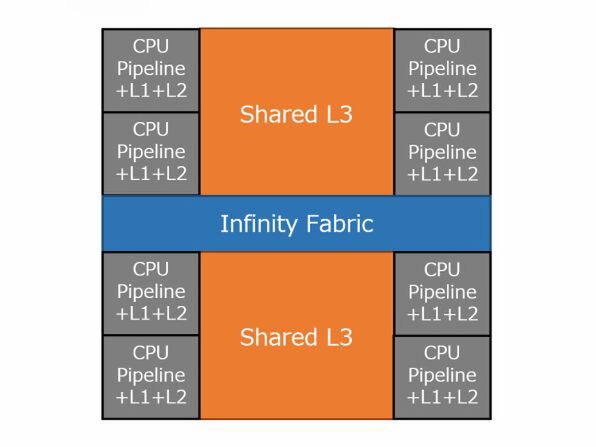

これを簡単に書けば、下図のような構成になる。

Ryzen、あるいはRyzen 2の場合、このインフィニティ・ファブリックはCPUダイの中だけで閉じているのでこれでも問題はなかったのだが、Zen 2ベースの場合はメモリーなどに対してもインフィニティ・ファブリック経由で接続することになる。

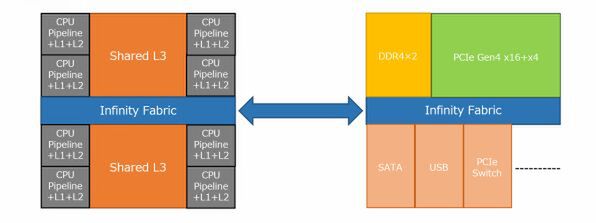

ということは、この構造を継承したとすると、下図のような構図になってしまう。これは果たして合理的かどうか? という話だ。

CPUダイの側とI/Oダイの側の2つのインフィニティ・ファブリックのスイッチが連携して動くとすれば、インフィニティ・ファブリックをまたいでのCPUコア間の通信がさらに遅くなることになる。

逆に連動していないとすれば、CPUコアからメモリーアクセスを行なう場合、CPUコア→CPUダイ側のインフィニティ・ファブリック スイッチ→I/Oダイ側のインフィニティ・ファブリック スイッチ→メモリーコントローラー、と2つのスイッチを挟むことになり、そうでなくても大きくなりそうなレイテンシーがさらに増えることになり、あまり賢明とは思えない。

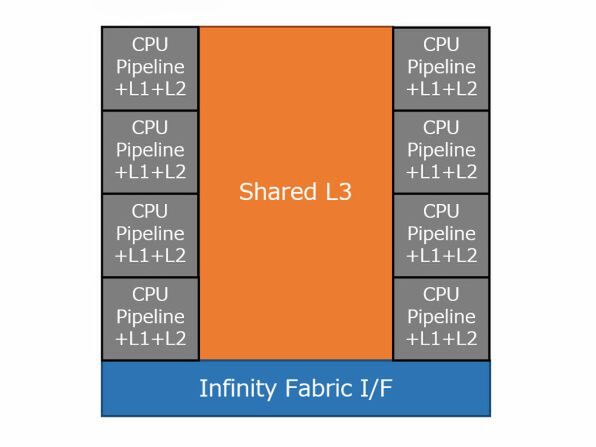

それもあって筆者は、Zen 2世代では下図のようにCCXが拡張されたのではないかと考えている。

つまりCPUコア同士はインフィニティ・ファブリックを介さず3次キャッシュ経由で直接接続されており、この3次キャッシュにインフィニティ・ファブリックのI/Fだけが用意されている。そしてインフィニティ・ファブリックのスイッチそのものはI/Oダイの側に集約されているという案だ。

そもそもなぜCCXが4コアベースなのかといえば、Raven Ridgeが4コアだからというのが答えになる。4コア製品が最小単位だからCCXは4コアベースとし、8コア製品はCCXを2つ搭載したわけで、もし最小構成が8コアならばCCXを8コアに拡張してもかまわないということだ。

もっともこの案にもいくつか欠点がある。最大のものは、これだと仮にRaven Ridgeの後継、つまり7nmで製造されるGPU統合RyzenがCPUとGPUをモノリシック(一体的)なダイで統合する場合にやりにくいことになる。また7nm世代でも、モバイルや組み込み向けに最小構成が4コアだとすれば、やはり8コアでCCXを作るのは無駄が多すぎる。

それとSenseMIはインフィニティ・ファブリック(正確にはScalable Control Fabric)をベースに構築されており、これのネットワークをI/Oダイ側に持っていって大丈夫なのか? というのが現時点では判断ができない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 - この連載の一覧へ