ロードマップでわかる!当世プロセッサー事情 第579回

Tiger Lakeの内蔵GPU「Xe LP」は前世代のほぼ2倍の性能/消費電力比を実現 インテル GPUロードマップ

2020年09月07日 12時00分更新

Xe LP利用するのはTiger Lake、DG1、SG1の3つ

さて、ここからもう少し具体的な話を。Xeには4つの製品カテゴリーがあり、このうちXe LPは最初のものがTiger Lakeに搭載された。またハイエンドであるXe HPCはPonte Vecchio向けにもう具体的なスペックが決まっているようだが、間に入るハイエンドグラフィック向けのXe HPGや汎用GPUであるXe HPに関しては、まだ“in the lab”という段階であり、具体的なスペックも公開されていない。

なぜかスライドでXe HPGだけずれている。ベースはGDDR6だそうで、今のところGDDR6Xという話ではなさそうだが、単にこのスライドがGDDR6Xの発表前に公開だったので書いてないという可能性もある

Xe LPであるが、これを利用するのはTiger LakeとDG1、それとSG1の3つである。連載577回でも少し触れたが、DG1はCES2020で明かされた、ゲーム開発者向けのビデオカードである。

ではSG1は? これはCDN(Contents Delivery Network)などで利用されるサーバに搭載するためのものだ。昨今はCDNといっても以前と異なり動画配信の比率が大幅に高くなっている。

ところが動画配信の場合、複数のビットストリームを生成して回線状況にあわせて自動的に変更したり、複数のコーデックに対応するなどのニーズが要求されるため、これをCPUで処理していると間に合わない。こうした用途向けに、GPUとしての性能は最小限(そもそもGPU的な要求がほとんどない)ながら、Media Sliceを強化した外付けタイプのカードをSG1として提供するという話であった。

実際この市場にFPGAを突っ込んだり専用アクセラレーターを開発する話はよく聞くところで、例えばEUは最小限だけどMedia Sliceが10個くらいあるような、GPUというよりも限りなく動画エンコーダー/デコーダー/トランスコーダー向けの製品が手頃な消費電力で提供されれば、ニーズは高いだろう。まだSG1のスペックなどは明らかにされていないが、多分そう遠くない時期に投入されると思われる。

Tiger Lakeに搭載されるXe LPは

Gen11のほぼ2倍の性能/消費電力比を実現

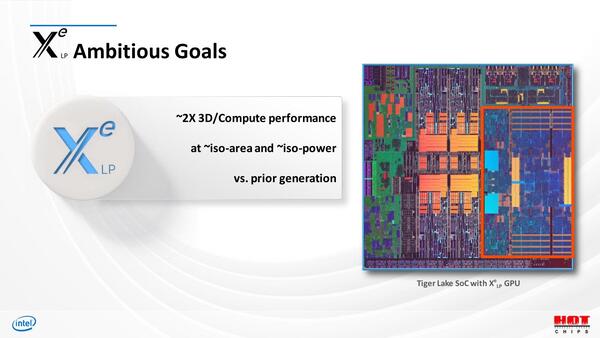

次はTiger Lakeの話だ。GPUのスペックは連載577回にまとめてあるが、Gen11とほぼ同じエリアサイズおよび消費電力で、ほぼ2倍の性能/消費電力比を実現したとする。

Subsliceは6つで、おのおのが16EUを搭載するので合計96EUである。またTexture Unitは最大48 Texels/clock、Pixel Backendは24Pixels/clockでの処理が可能となっている。

連載577回のスライドでは3次キャッシュが3.8MBになっているが、アーキテクチャー的には3次キャッシュは16MBまで搭載可能であり、おそらくはダイサイズとの兼ね合いなどから3.8MBに削減しての実装となったと思われる。ただ、どうしてこんな半端な数字なのかちょっと聞いてみたいところである。

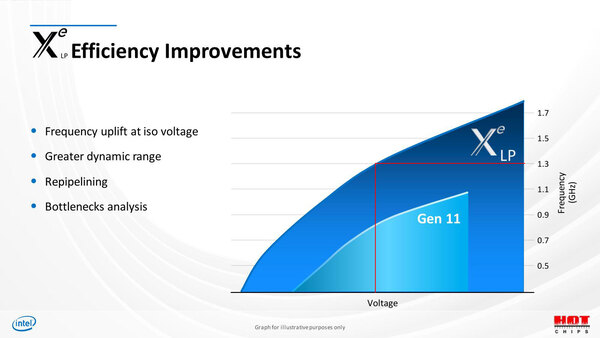

動作周波数は連載577回で、最大1.65GHzあるいは1.85GHzあたりまで引っ張れると説明したが、Core i7-1165G7のスペックを見ると1.3GHz止まりになっており、あまり上まで引っ張る感じになっていないところだ。

実際のところ、あまり動作周波数を引き上げてもメモリー側が追い付かないので、このあたりでバランスを取ったのかもしれない。

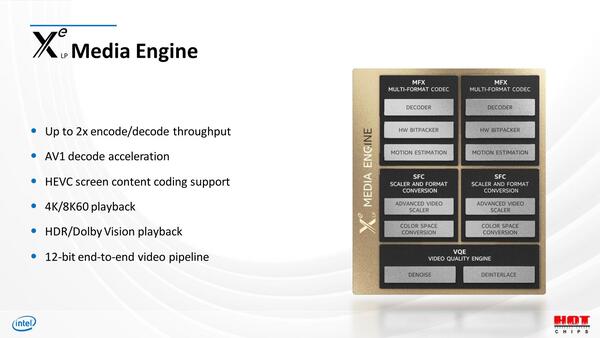

Media Sliceは1個だけ搭載されるが、MFX/SFCともにダブル実装で、従来比2倍のスループットとされる。

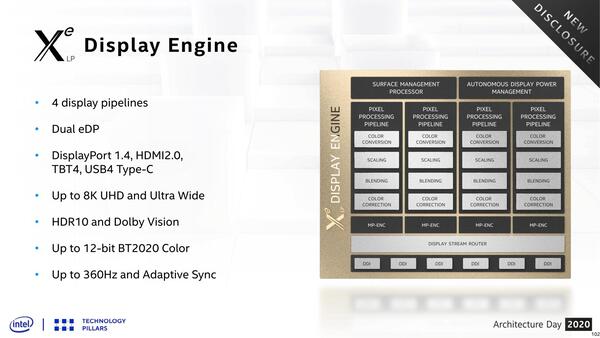

ちなみにHot Chipsでは説明が省かれたが、Architecture DayではDisplay Engineの詳細も公開されている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ