Lake Crestの後継となる

深層学習用プロセッサーSpring Crest

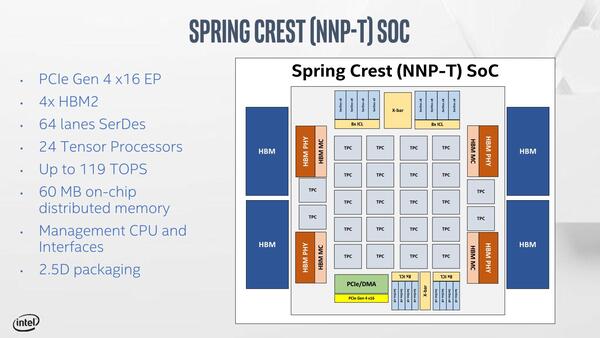

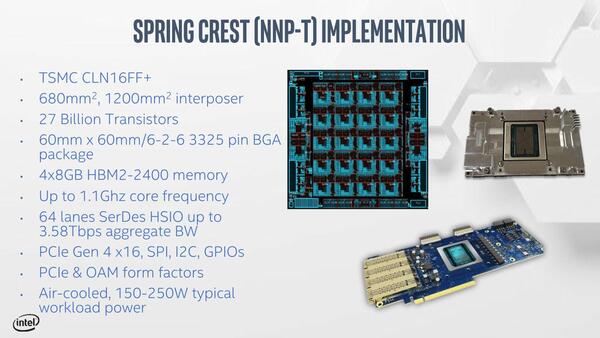

さてそのSpring CrestことNNP-Tは、2つのTensor Coreを組み合わせたTensor Core Cluster(TPC)を24個搭載。PCI ExpressもGen4としたほか、メモリーを2.5MBに増やしている。製造プロセスはTSMCの16FF+を利用、ダイサイズは680mm2とされる。

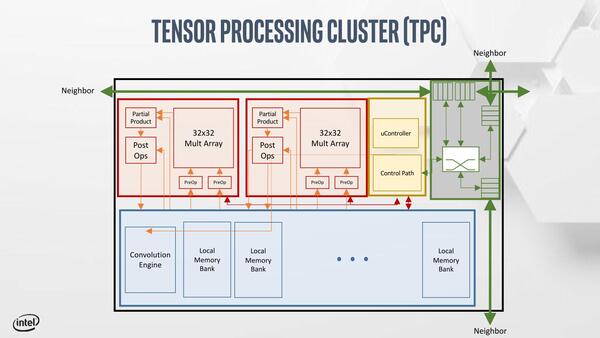

下の画像はTPCの内部構造で、2つのTensor Processorとローカルメモリー、Convolution Engineなどを共有する構造になっている。

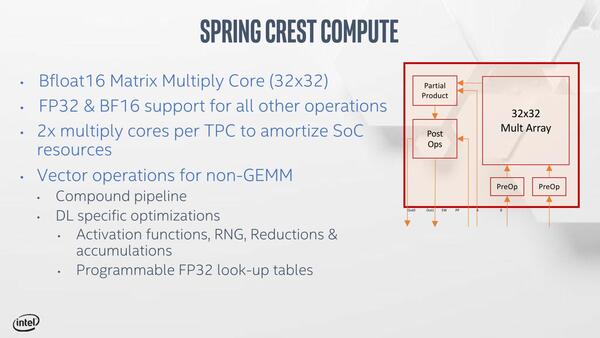

個々のTensor ProcessorはBFloat16の演算ユニットを32×32個アレイ状に配した構成で、1サイクルあたり2048演算(乗算+加算)が可能である。

1TPCあたりなら1サイクルあたり4096演算。これが24個で、1.1GHz駆動ということで 1.1GHz×24×4096=108.1344TOPsとなる。

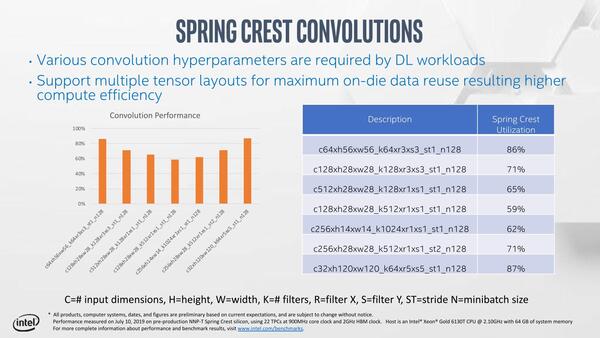

さらに、TPCの共有部にはConvolution Engineが専用に搭載されており、これは上の画像のCompute Unitとは並行して稼働するようなので、これの処理分も含めると119TOpsという数字になるのだと思われる。

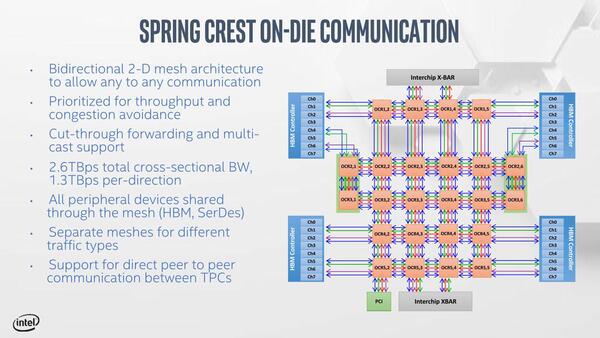

なおそれぞれのTPCは2Dメッシュ構成での接続になっており、すべての周辺機器やI/Oに均一にアクセス可能になっている。

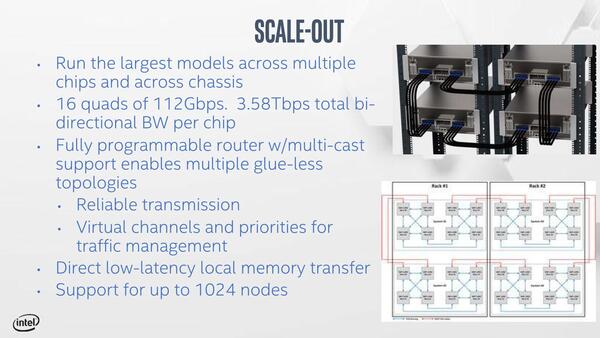

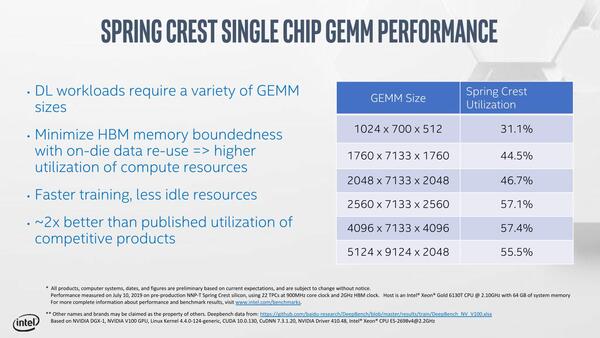

またスケーラビリティーにも配慮されており、最大1024ノードまでの接続が可能とされる。ちなみに性能の一端も公開された。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ