AI推論に不向きというx86の弱点を補うため

AI向けコプロセッサーを内蔵

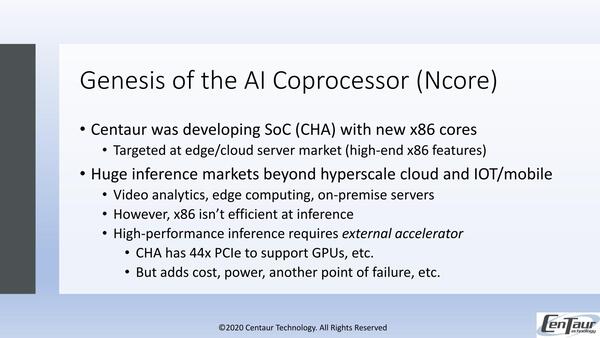

CHA+Ncoreの開発動機は下の画像の通り。もともとのCHAは、ZhaoxinがKX-6000シリーズとして提供しているものの後継を目指したSoCだったようで、ターゲットはサーバー市場である。

CHA+Ncoreの開発動機。CHAそのものは汎用で特にAIに向けたものではなく、例えばEdge Compute Serverを構築したければ、44レーンのPCI ExpressにそれこそNVIDIAのTeslaを4枚装着して、あとは10GbEカードなどをやはりPCI Expressでつなぐといった形を想定していた模様

といってもCentaurの場合は企業向けというよりも、エッジサーバーやクラウド向けで、どちらもそれほどの高い性能は必要ない。ここに向けて8コアのSoC構成だったのがオリジナルのCHAである。ただx86そのものはそもそもAIの推論に向いてないし、もっと言えば学習にも向いていない。

ではどうするか、というのは各社各様である。AMDは「推論も学習もGPUでやった方が効率が良い」というスタンスで、今のところCPU側にそれを取り込む計画はない(と言いつつも、トレンドにあわせて少しづつサポートするデータ型を増やすといった対応はしているが)。

逆に積極的なのがインテルで、AVX512のニューラルネットワーク拡張(AVX512VNNI)やCooper LakeでのBfloat16のサポートなど、本来AI処理に不向きなx86を力業で向く構造にしてしまっている。

これに対してCentaurは、素直にAI向けコプロセッサーを内蔵するという方法を選択した。

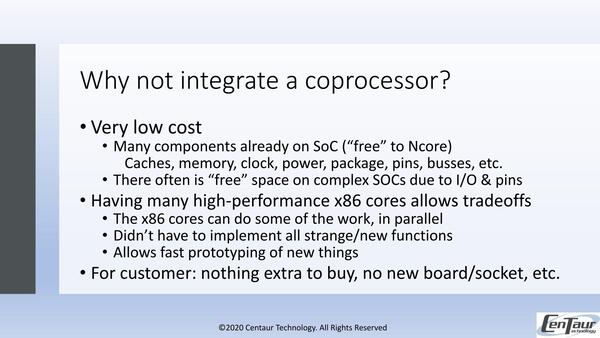

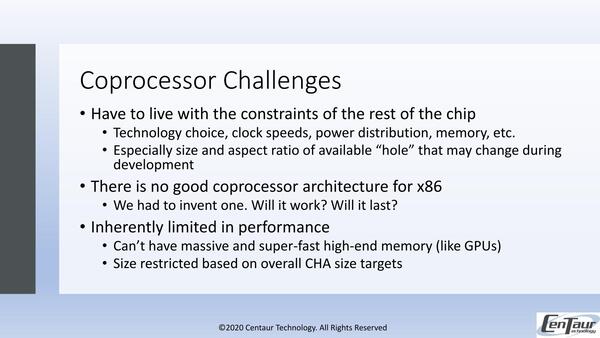

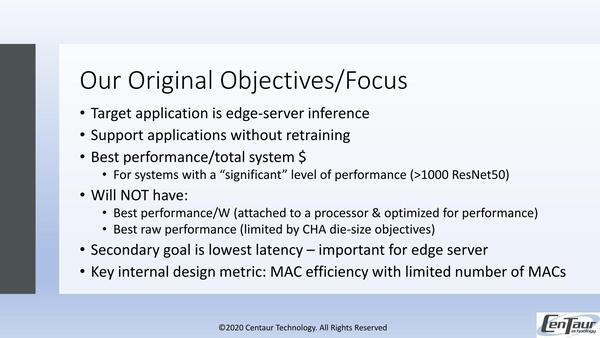

もちろんこの方式でもいろいろチャレンジはあるわけで、その結果としてCentaurはコストあたり最大の性能を第一目標、低いレイテンシーを第二目標に定めた。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ