X570チップセットに

第2世代Ryzenを載せたときの挙動

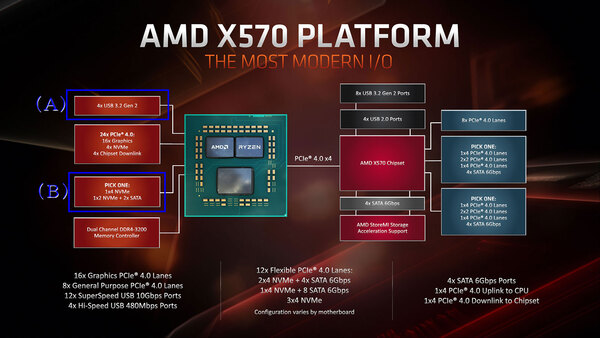

次にチップセット周りについて。連載513回の最後で、X570に第2世代Ryzenを装着した場合にどういう振る舞いになるのか、という点が不明だとしたのだが、これについて確認が取れた。

まず上の画像の(A)にあたるUSB 3.2 Gen2×4であるが、これは第2世代Ryzenを搭載した場合、USB 3.1 Gen1相当(USB 3.2 Gen1といっても良いが、要するにUSB 5Gbps相当)にダウンするとのこと。

次いで(B)の、1×4 NVMeに関しては第2世代Ryzenでは無効になるという話であった。おそらくではあるが、第2世代RyzenのCPUピンにはそもそもこの1×4 NVMe向けのPCIeの信号が出ていないのではないかと思われる。

またGPU接続用のx16のPCIeレーンも、X570との接続用のx4 PCIeレーンも当然Gen3相当になり、この場合X570から出るPCIeもすべてGen3相当になるという話だった。

ただこの場合でも、チップセットから出る8ポートのUSB 3.2 Gen2ポートはそのままUSB 3.2 Gen2として有効とのことであった。これは妥当な構成なのではないかと思われる。

メモリーはDDR4-5133まで可能

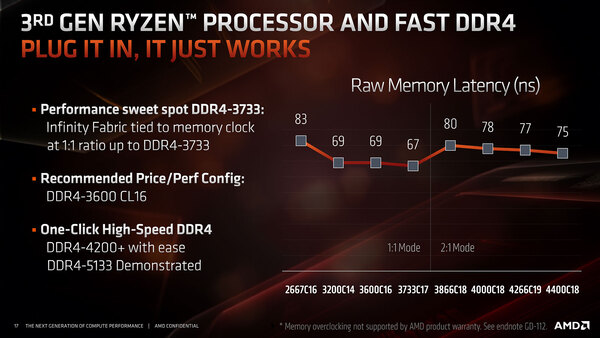

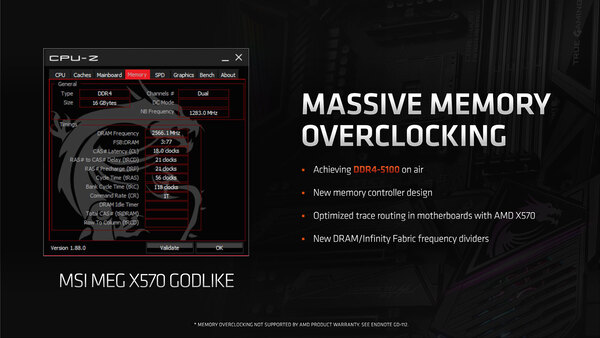

チップセットの話が出たところでついでにメモリーコントローラーの話もしておこう。第3世代Ryzenは、定格がDDR4-3200まで、という話は連載513回でレポートしたが、実際はというとDDR4-4200あたりまでは軽く行けて、DDR4-5133までは可能という説明があった。

ここに出てくる1:1Modeと2:1Modeであるが、これはメモリークロックとインフィニティーファブリックのクロック比である。

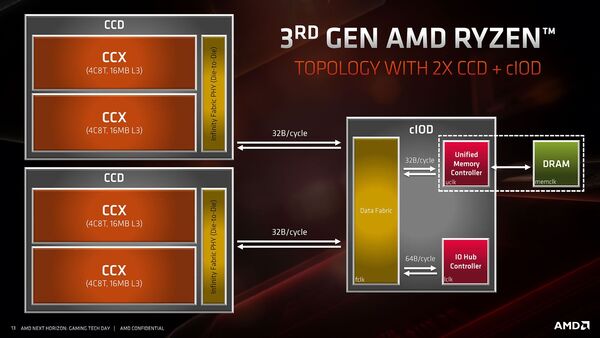

前回の記事の図で、I/Oチップレット(cIOD)側を見ると、メモリーのクロック(memclk)とメモリーコントローラーのクロック(uclk)、それとデータファブリックのクロック(fclk)が別々のクロックソースになっていることが示されている。

1:1 Modeの場合、memclkとuclkが連動し、ということはuclkとfclkも連動するために、あまりmemclkを上げすぎるとインフィニティーファブリックのスピードが上がりすぎて動作しなくなる。

そこでDDR4-3866(つまりmemclkが1933MHz)以上の場合、uclkとfclkの比を2:1にすることで、インフィニティーファブリックの速度が上がりすぎないようにできるという話である。これを利用すれば、DDR4-5133も夢ではないというわけだ。

この連載の記事

-

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 -

第851回

PC

Instinct MI400/MI500登場でAI/HPC向けGPUはどう変わる? CoWoS-L採用の詳細も判明 AMD GPUロードマップ -

第850回

デジタル

Zen 6+Zen 6c、そしてZen 7へ! EPYCは256コアへ向かう AMD CPUロードマップ -

第849回

PC

d-MatrixのAIプロセッサーCorsairはNVIDIA GB200に匹敵する性能を600Wの消費電力で実現 -

第848回

PC

消えたTofinoの残響 Intel IPU E2200がつなぐイーサネットの未来 -

第847回

PC

国産プロセッサーのPEZY-SC4sが消費電力わずか212Wで高効率99.2%を記録! 次世代省電力チップの決定版に王手 -

第846回

PC

Eコア288基の次世代Xeon「Clearwater Forest」に見る効率設計の極意 インテル CPUロードマップ - この連載の一覧へ