ダイの構造から考えられる

3次キャッシュの大容量化

CPUダイが78mm2、I/Oダイが132mm2という面積をどう考えるかであるが、もともとのZenのダイ(210mm2)と比較するとかなり大きい、というのが筆者の偽らざる印象である。

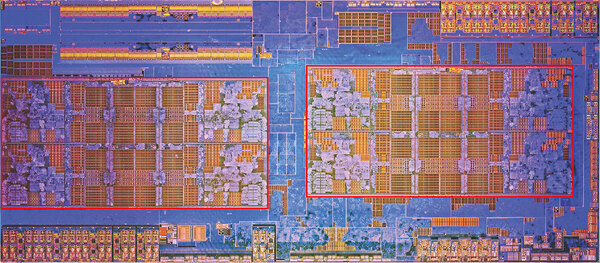

下の画像はZenのダイの内部であるが、赤く囲んだCCX(Core Compulex:CPUコアのクラスター)の面積はだいたい47.5mm2ほどになる。これが2つで95mm2という計算である。

連載484回でも示されているように、TSMCの7nmプロセスはラフに言ってGlobalfoundriesの14nmプロセスの倍のトランジスタ密度(配線密度と言っていないところが肝ではあるが、その話はおいておく)なので、このCCXの構造そのままに7nmに移行した場合、それこそ47.5mm2程度で収まらないとおかしいことになる。

実際にはFPUの帯域を倍増する)などの変更もあるため、もう少し大きくなるかもしれないが、それでも50mm2強といったところだろう。

このZen 2の構造の場合、CPU側のダイは8コア分のCCX+インフィニティ・ファブリックのPHYのみが搭載される構造になる。するとインフィニティ・ファブリックのPHYが27mm2も占めることになってしまう。いくらなんでもこれは大きすぎる。

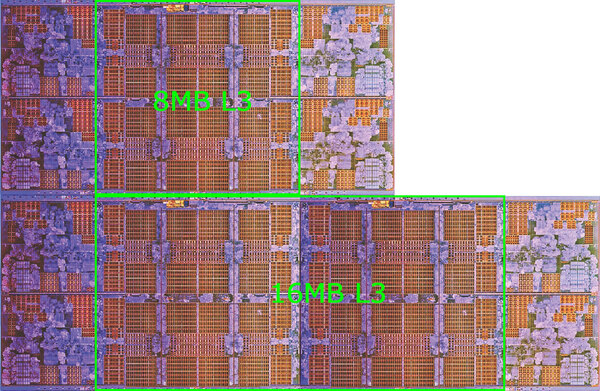

では他になにか拡張があり得るか? 1つ可能性としてあるのは、3次キャッシュの大容量化である。現在はCCXあたり8MB(つまりダイあたり16MB)になっているが、これを倍増したらどうなるか? というのが下の画像である。

この16MBの3次キャッシュ(つまりダイあたり32MB)の構成の場合、CCXあたりの面積は14nmで72.2mm2ほどになる。7nmを利用すれば、CCXが2つで72~73mm2というあたりになり、するとインフィニティ・ファブリックのPHYが5~6mm2という計算になる。

少なくともインフィニティ・ファブリックが27mm2を占めるというストーリーよりもこちらの方がはるかに現実味があるだろう。

なぜ3次キャッシュを倍増させるかといえば、FPUの256bit化への対応である。つまり1サイクルあたりが扱うデータの量がZen世代から倍増しており、これに向けてロード/ストアーユニットも256bit化されているわけだが、本来ならばこれにあわせてメモリーアクセスの帯域も倍増させないとメモリーがボトルネックになる。

ただこれを解消するためにはDDR4のチャネル数を倍増させないといけず、これは難しい。そこで解消はされないにしても緩和する方法が3次キャッシュの大容量化である。

AMDは公式には3次キャッシュの容量についてなにも言っていない(増やすとも増やさないとも言及していない)が、ダイサイズから考えるとけっこうありそうな気がする。

I/Oダイサイズの132mm2は

妥当な数値

ついでにI/Oダイについても話をしよう。先の計算では、14nm世代でCCXが1つあたり47.5mm2なので、CCXを2つ除いた残りの部分のダイサイズは115mm2程度になる。

Zen世代のダイになく、Zen 2世代のI/Oダイにあるものはインフィニティ・ファブリックのI/Fである。前述の3次キャッシュ倍増の試算が正しいとすれば、インフィニティ・ファブリックに要するダイ上のエリアサイズは7nmプロセスでだいたい5mm2程度。14nmで倍増するとしても10mm2ほどになる。

そうなると、I/Oダイにインフィニティ・ファブリックのI/Fを2つ搭載すると、合計のダイサイズは135mm2程度になる計算で、上に示したおおむね132mm2、という寸法にかなり近くなるかたちだ。

実際にはI/Oダイでは他にPCI Express Gen3→PCI Express Gen4への移行といった要件もあるが、こちらはダイサイズそのものが大きくなる要素はあまりなく、PHYの周辺だけドライバー部でトランジスタ数が多少増える程度であろう。

逆にZenの世代ではPCI Expressはインフィニティ・ファブリックと共用の形になっていたが、Zen 2ではPCI ExpressのPHYはPCI Expressのみなので(EPYC用のI/OダイはCCIXへの対応が必要だが、Ryzen向けにはCCIXのサポートはおそらくないだろう)、むしろエリアサイズが減っている可能性すらある。そう考えると、132mm2という寸法は妥当なのではないかと思う。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ