今回のネタはHBMだ。第1世代のHBM1はAMDがRadeon R9 Furyシリーズに採用した程度でしかないが、第2世代のHBM2はAMDのRadeon Vega、NVIDIAのTitan VといったGPUだけでなく、Xilinxやインテル(旧Altera)のFPGAなどですでに採用されており、今後はさらに採用例が増えることが予定されているなど幅広く使われることが決まっているメモリーである。

HBMにつながる基本的なアイディアは、「よりメモリーを広帯域に接続するために、バス幅増やそう」というものだ。そもそもメモリーの帯域を増やすためには以下の2つがある。

- 信号速度を引き上げる

- バス幅を広げる

これまでの主流は信号速度を引き上げるほうで、SDRAM(100~166MHz)→DDR(200~400MHz)→DDR2(400~1066MHz)→DDR3(800~1866MHz)と来て、DDR4世代では2133~4266MHzまでが視野に入っている。

これはグラフィックス向けも同じで、GDDR3世代では4GMHzだった信号速度は、GDDR5世代では8GHzに達し、GDDR5Xで12GHz、GDDR6では16GHzに達する。バスの幅は変わらないため、速度にあわせて帯域が広がったわけだ。

ただ、実際には「もっと帯域が欲しい」というニーズは常にあるため、例えばGeForce GTX 780などはGDDR5を384bit幅で接続している。また、Core-XシリーズのうちSkylake-SPコアのものはDDR4が4ch構成になっていたりする。

つまり速度を引き上げるといっても限度があるわけだ。おまけに、速度を引き上げると往々にして消費電力もグンと上がりがちになる。そこで逆転の発想で、「信号速度そのものは下げるが、バス幅を大幅に増やそう」という考え方が出てくる。

製造コストが高すぎて普及しなかった

バス幅拡張技術「WideIO」

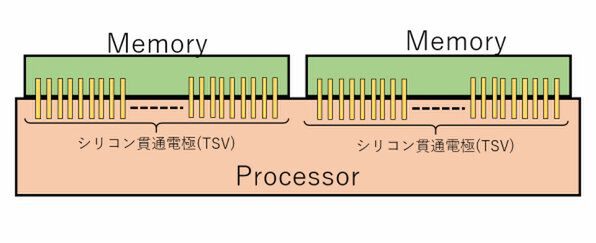

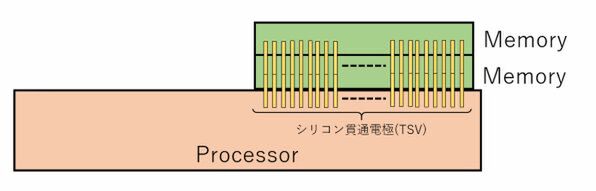

最初に登場したのがWideIOという規格である。これは下図のように、プロセッサーの上面にメモリーを置き、間をTSV(Through Silicon Via:シリコン貫通電極)でつなぐというものだ。

1つのWideIO Memoryは512bit幅のバスに200MHzの信号を通す予定になっており、メモリー1個あたりの帯域は100Gbps(12.5GB/秒)に達する。より広帯域が必要なら上図のように並列につなげばいいし、帯域よりもメモリー容量が必要な場合は下図のように積層することも可能だった(仕様上は4つまで積層可能とされた)。

信号ピンの数は多いが、信号そのものが200MHzと比較的低速なので、データ転送の消費電力そのものは低く抑えられるということで、モバイル向けに利用されると思われた。

ところが実際には採用例は「0」だった。理由は2つ。1つはTSVの構築が無茶苦茶高コストになること。もう1つはモバイル向けであってもプロセッサーからはそれなりに熱が出るわけで、メモリーチップはこの熱で炙られることになり、動作に支障が出る恐れがあることだ。

特に1つ目の問題がシビアであった。少し前の試算だが、通常のメモリーチップにTSVを作りこむと、原価が3~4倍に跳ね上がるという話だった。しかもメモリーチップだけでなくプロセッサーの側にもTSVを設けないといけないため、トータルでのコストが1桁上がりかねないと予測された。これはさすがに採用するには厳しい数字である。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ