今年のARM Techconはセキュリティマニフェストが出るなど、かなり変則的な基調講演だったが、最終日にはようやく技術系の基調講演が行なわれた。

1兆個のIoTデバイスがすべてボタン型電池を使ったとすると、10万9000トンのリチウムが必要になるが、現在の年間のリチウム生産量は3万2500トンしかないのだ。もちろんリチウムは電気自動車用のバッテリーなどでも大量に用いられているのにだ

これからは微細化が困難に

積層型の半導体がスマホのSoCにも?

最終日の基調講演に立ったのは、ARM社フェローのGreg Yericと、同じくDirector of TechnologyのRob Aitken。Greg Yericは「Process Technology Limbo」と題して、今後のプロセスなどの方向性を概観するものだ。

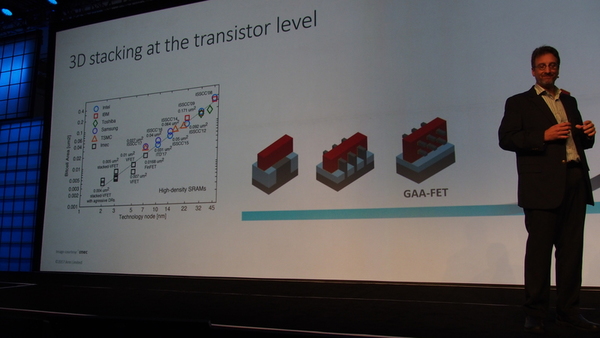

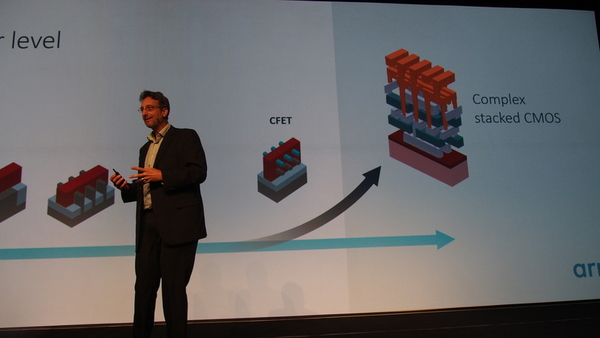

プロセスが微細化したたため、20nmプロセスあたりからトランジスタ自体の構造を変える必要があるなど、製造技術だけでなく、トランジスタ設計などを併用してプロセスを更新していく必要が出てきた。著名なのはFinFETやトライゲートトランジスタなどと呼ばれるものだ。FinFETは、ヒレ(Fin)状のゲート構造をもつFETなのだが、そのフィンの数を増やしたり、ソース・ドレインがフィンを貫通する構造を変えるなどの工夫が現在では行なわれている。その発展型が、フィン状のゲートがソース・ドレインを上下、左右完全に覆うような構造のGAA(Gate All Around)FETだ。

その先には、CFET(Complementary FET)という構造もある。これは、nチャネル型のFETとpチャネル型のFETを組みあわせて1つのゲートを共有させるものだ。GAAをゲートのところで上下に組みあわせたような構造となる。一般にCMOS回路では、nチャネルとpチャネルのFETを組みあわせて使うため、こうした構造を取ることが可能になる。

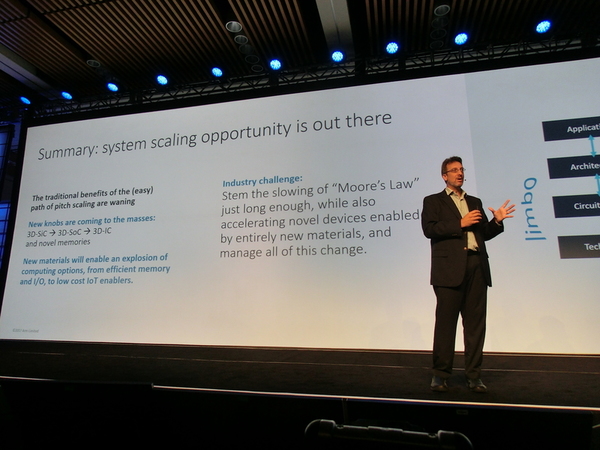

Yeric氏は、こうした半導体製造の現状を「Limbo」と呼ぶ。Limboとは「中間状態」という意味だが、それと別に「地獄の辺土」という意味や棒の下をくぐるいわゆる「リンボーダンス」のことでもある。小さくすることだけを主に考えていた20nmまでの時代とはもう違うのだという意味があり、この先には、問題が多数見えており、大変になるということなのだろう。

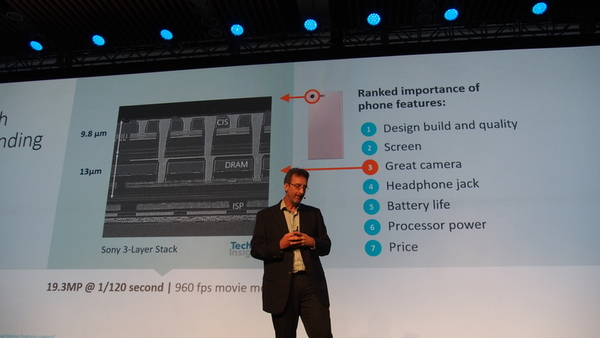

また同氏は、ソニーのスマートフォン用カメラデバイスを例に、2.5Dがメインストリームに入り、今後は3D-Stacked ICが主流になるだろうとした。ソニーのカメラデバイスは、CMOSイメージセンサーとDRAM、画像処理部を縦に重ねて作られている。画素数が高くなり、イメージセンサーデータをシフトしながら順次読み出していく方法は困難になった。

そこで、イメージセンサーのデータを並列同時読み出しとして直接DRAMに入れ、これを画像処理部が読み出して処理するという構造が必要になった。このために、3層のスタックを実現したのがソニーのカメラデバイスというわけだ。こうした手法は、いずれスマートフォンなどのSoCにも波及するとYeric氏は語る。

現状、各層を別々に作り、これをあとから組みあわせるという手法が使われている。というのは、半導体の種類ごとに製造プロセスに違いがあり、まとめて積層していくわけにはいかないからだ。このため、スタックして作られるデバイスは3D(3次元)ではなく、2.5次元、つまり2.5Dだという考えもある。Yeric氏は、こうした3D-SiCはさらに発展して3D-SoCになるとした。

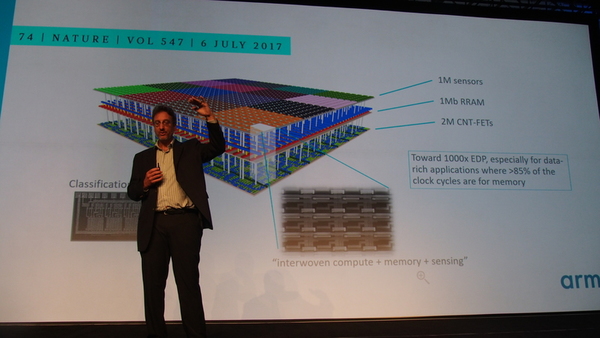

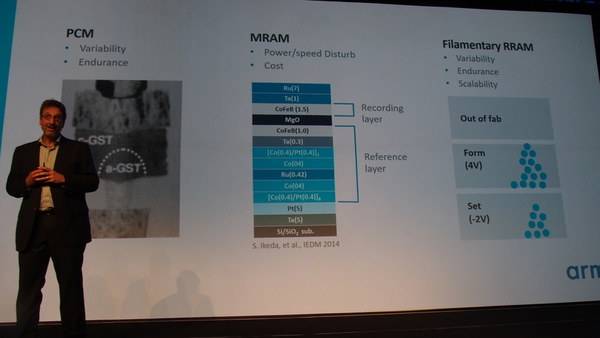

メモリについては、「スーパーメモリ」はないが、DRAMを置き換えうるeNVMがあるとした。PCM(Phase Change Memory。相変化メモリ)、MRAM(Magnetoresistive RAM。磁気抵抗メモリ)、Filamentary RRAM(フィラメント型抵抗変化メモリ)などがその候補だという。こうしたeNVMとSoC回路、そしてセンサーを組みあわせたものを同氏は、3D-SoCと呼ぶ。さらにGAA-FETやCFETの先に、トランジスタを縦向きに作るという方向があり、さらに縦になったトランジスタを使ってCMOS回路全体を縦向きに作るというアイディアもある。つまり真の3次元構造をもつ「3D-IC」も可能になるというわけだ。

現在は、こうした構造と製造プロセスが同時に変化していく「Limbo」であり、さらにその先には、露光の限界、電子の制御の限界というもっと難しい問題が待ち構えているわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります