ソフトバンクの孫氏にちょっと話題を持って行かれた感じもある今回のARM TechConだが、メインの話題は新しい組み込み向けプロセッサのCortex-M23およびM33である。Cortex-Mシリーズは、コンピュータ以外の機器で利用する「組み込み」用のプロセッサだ。

家電などプロセッサ(コントローラーと呼ばれることが多い)を組み込んだ製品は少なくないが、それ らの多くがこのCortex-Mシリーズを利用している。

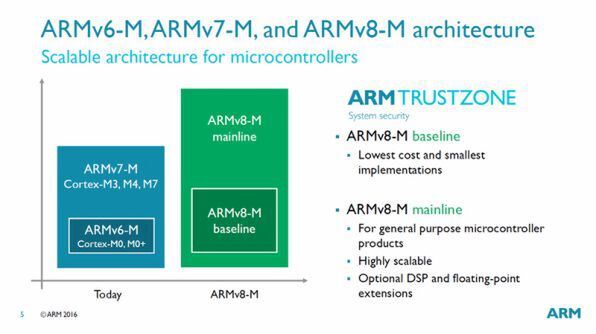

2015年のARM TechConでは、その新しいアーキテクチャとなるARMv8-Mを発表した。スマートフォンなどで利用するARMv8-Aは、64bitアーキテクチャを含むが、ARMv8-Mは32bitのまま。しかし、これまでの組み込み向けプロセッサには無かった“セキュリティ”機能が強化されており、クラッキングやウイルスといった問題に対して強くなっている。

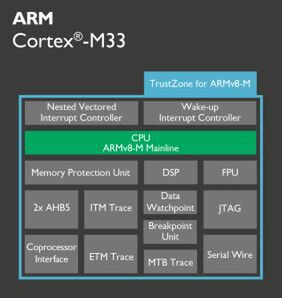

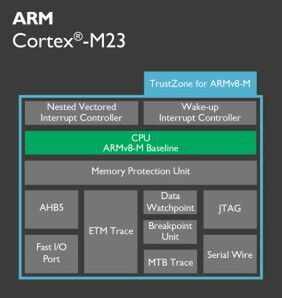

まずCortex-M33は、従来のCortex-M3またはM4に相当し、Cortex-M23は、Cortex-M0+に相当する。ARMv8-Mでは、最低限の部分を定義したBaselineとフル定義のMainlineかあるが、Cortex-M23はbaseline、M33はMainlineを満たす。

ARM社の製品は、SoCを作るための設計データや特定のファウンダリーで製造するためのハードマクロ(簡単にいうと半導体製造のためのマスクパターン)などだが、これらはまとめて「IP」(知的財産)と呼ばれている。

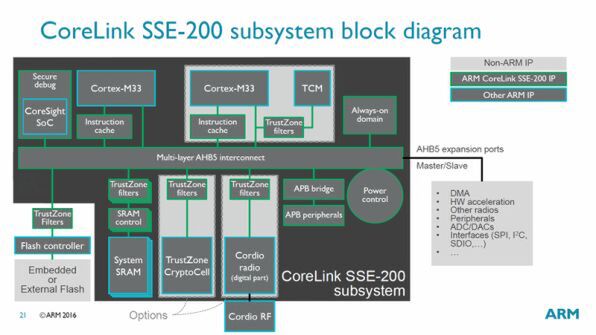

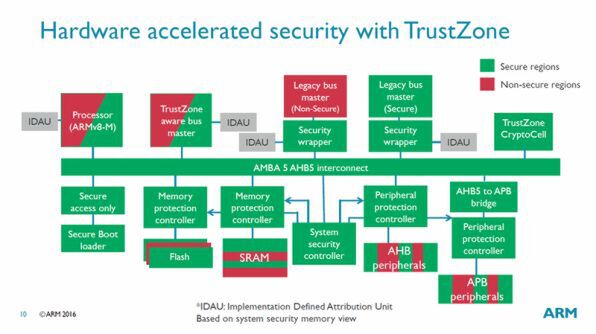

Cortex-M23/33コアに合わせ、SoC内のインターコネクトを作るためのIPとしてSIE-200と、インターコネクトや暗号化回路、IoT用の無線通信回路(Cordioというブランド名を持つ。ただしデジタル回路部分のみで高周波回路部分は含まない)などのIPやmbed OS、ドライバ類を含むSSE-200という製品も同時に発表されている。

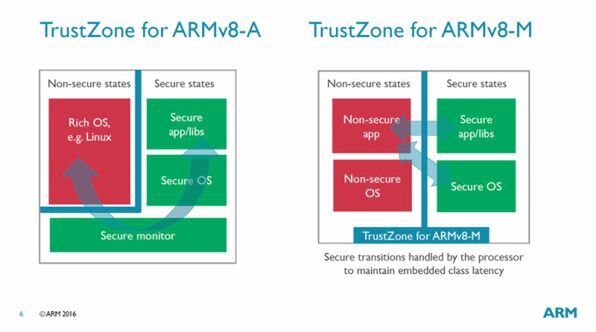

ARM社のプロセッサのセキュリティ機能はTrustZoneと呼ばれているが、スマートフォンなどに利用するCortex-A(ARMv7/v8-A)と組み込み系のCortex-M(ARMv8-M)では、セキュリティモデルや実装に違いがある。

アプリケーションプロセッサであるCortex-AのTrustZoneでは、セキュリティモニターを経由してセキュアゾーンとノンセキュアゾーンを行き来する。また、OSでメモリ管理や仮想メモリなどが行なわれているため、他のプロセスのメモリを見ることも困難だ。

これに対して、組み込み系では、OSが入らない場合もあり、また仮想メモリもない。このため、ARMv8-Mでは、System Secury Controlerと呼ばれるハードウェアが基本的なセキュリティを管理し、システム全体を「セキュア」領域と「ノンセキュア」領域に分割する。ソフトウェアはもちろん、プロセッサコアや周辺回路、メモリなどのハードウェアにも「セキュア」なものと、「ノンセキュア」なものに分割される。

ソフトウェアから見ると、セキュアとノンセキュアの遷移は、割り込みか、セキュア側で予め定義されたエントリポイントの呼び出ししかできない。セキュリティの大部分をハードウェア化し、ソフトウェアの介入を最小になるようにしているのは、組み込み系の場合、CPU性能が高くないこともあるのに対して、リアルタイム性や一定時間内の応答が要求されるからだ。

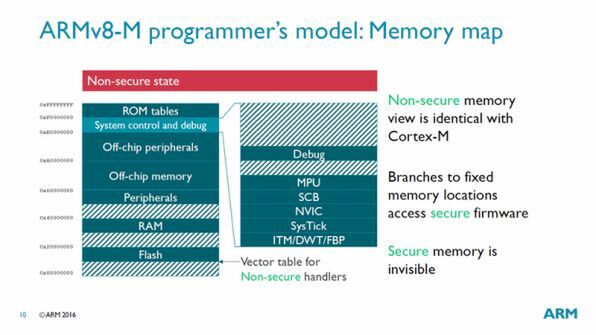

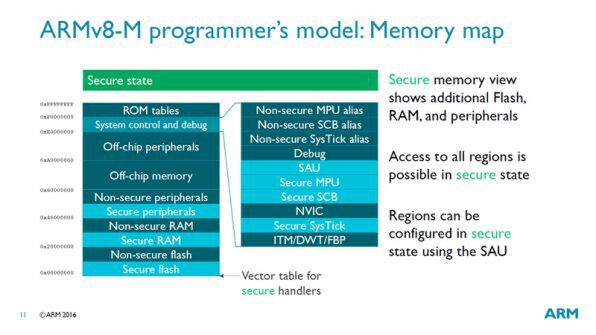

ARMv8-MのTrustZone(以後、便宜的にTrustZone-Mと表記する)では、メモリをセキュア、ノンセキュアに分割するが、仮想メモリを利用しないCortex-Mでは、物理メモリをアクセスする。しかし、SoC内では、絶対番地で指定された用途の決まった領域がある。

たとえば、Cortex-Mでは、起動時や割り込みが発生した場合にゼロ番地から始まるベクターテーブル(アドレス表)を使って、対応するルーチンを実行する。前述のようにプロセッサコアにも「セキュア」と「ノンセキュア」がある場合、ここを共有してしまうと問題が起きる。

まず、電源オンやリセットによりシステムが初期化されると、最初に起動するのはセキュアなプロセッサコアとなり、これは、物理メモリのゼロ番地にあるベクターテーブルを使って起動が行われる。セキュアコアは、SoCやセキュリティ関係の設定をし、これにより、System Security Controller(SSC)が設定され、以後のセキュリティ機能は、このSSCが中心になる。CPUコアからメモリへのアクセスに関しても、セキュア側のコアかどうかを判断して適切なメモリ保護を行なう。

これにより、ノンセキュア側のコアは、セキュア側に属するメモリ領域へのアクセスができなくなる。もともと、組み込み系では、アドレス空間がすべて埋まっているわけではなく、ところどころに何もない領域が挟まる。どこに何があるのかは、SoCの仕様であり、基本的には、SoCの仕様に合わせてプログラムを作るため、セキュア側のメモリやメモリマップされたデバイスが存在しないようになっても特に問題はない。仮想アドレスのようにアドレスが連続しているように全体をマッピングする必要はないわけだ。

しかし,前述のベクターテーブルなどは、CPUアーキテクチャで定義されている利用方法の決まったアドレスであるため、そのままでは問題がある。TrustZone-Mでは、ノンセキュアコアのベクターテーブルの位置が変わる。

また、メモリ空間の上部にあるシステム制御用のレジスタは、やはりノンセキュアとセキュアでは違って見える。ただし、セキュア側からは、ノンセキュア側のレジスタ値を別のアドレスでアクセスすることが可能だ。

Cortex-M23/33では、高いセキュリティ機能を手に入れたが、そのためには、TrustZone-Mに対応したコードを追加する必要があり、また、ノンセキュア側でも仕様の変更があるため、ある程度の変更が必要になる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります