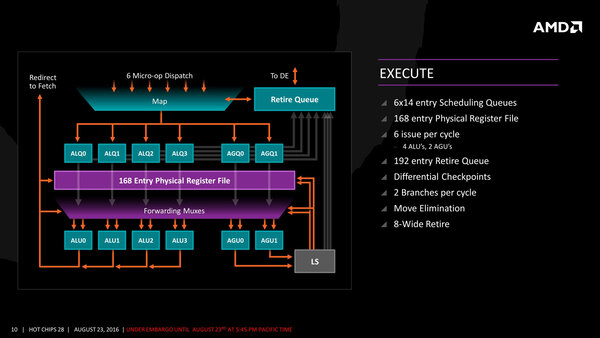

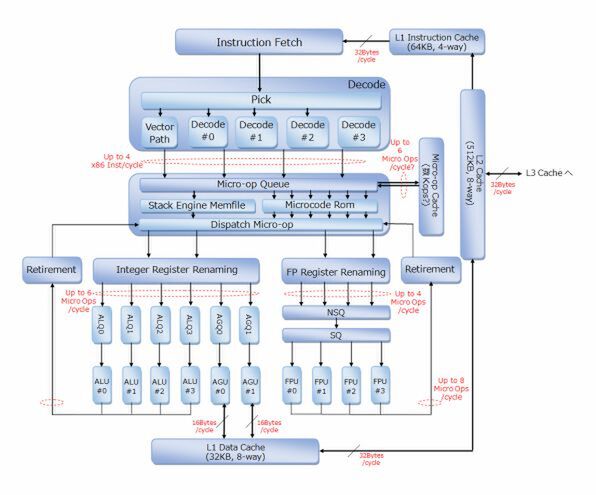

次がALU/AGUの実行段である。ここに関してはそれほど意外さはないのだが、最大8 MicroOpのRetirementをサポートしているあたりはかなり強力な印象である。

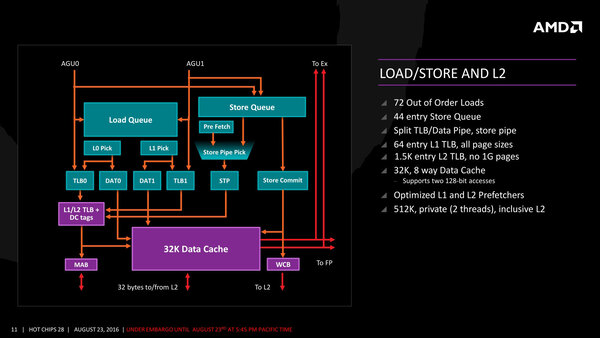

またキューの数も192と多く、このあたりはSkylakeと比較しても遜色はない。Load/Storeユニットの構造は下の画像のように一見複雑に見えるが、それほど不思議なものはない。

Skylakeに比べるとピーク性能(SkylakeはLoad/Storeユニットを合計4つ搭載)は半減するが、Haswell/Broadwellとは同等で、そもそもSkylakeの4ユニットのLoad/Store Unitは512bit幅のAVX-512命令(Core iグレードでは無効で、Xeonでのみサポート)を前提としたものなので、これをサポートしないZenには無関係であり、逆に言えばAVX-512を除くオペレーションではSkylakeと互角の性能ではないかと思われる。

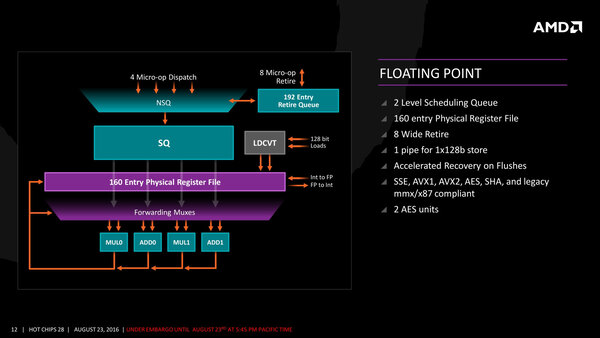

一方浮動小数点側の実行段では、Micro-OpのDispatchの後、2回のスケジューリングが行なわれることが今回明らかにされている。またこちらも8命令のRetirementがサポートされている。

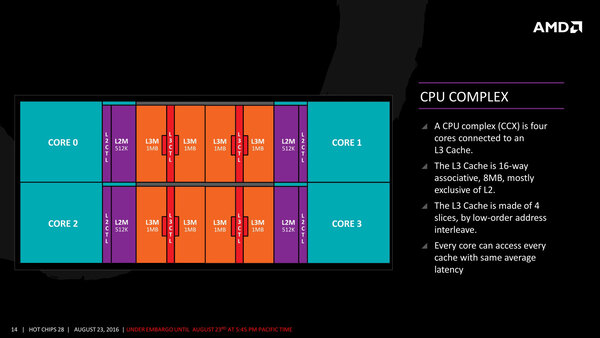

それと、3次キャッシュに関してだ。連載370回の時点でははっきり記載されていなかったが、今回明確に1次/2次キャッシュはInclusive、3次キャッシュはExclusiveの構造になっていることが示された。

また4つのコアと1MB×8のブロックを組み合わせて1つのCPU Complexが形成されることも明らかになった。ちなみにこのCPU Complex内はFabricで接続されているそうである。

Summit Ridgeは8コア構成なので、CPU Complexが2つ搭載されている格好だが、このCPU Complex同士はハイパートランスポートではない独自のリンクで接続されるそうだ。

最後に訂正を1つ。連載370回で「おそらくは(不要ブロックの電源供給をもカットする)Power Gatingも複数レベルで実装されているだろう。」と書いたが、説明の中でPower Gatingは現段階では実装されていないことが明らかにされた。

ただこれは、Power Gatingが必要ないほどGlobalFoundriesの14LPPのリーク電流が少ないという話なのか、それともなにかしらの技術的な理由によりPowerGatingが実装できないという話なのか、あるいはその他のなにか理由があるのか、は現時点では不明である。

以上の訂正をもとに、図を反映してみた。個人的な見解は、これでZenとK12の切り分けがはっきりしてきたと思う。K12は、マイクロコードRomとその上が全部入れ替えになり、一方でDispatchから下側は完全にZenと同一形態を取るであろう。

x64命令とAArch32/64では当然デコーダーの構造が異なる(特にAArch32をサポートするのが必須なので、この部分の作りこみが結構大変そう)ため、ピックやデコードの構造は当然異なるし、Vector Pathも作り直しだろう。Micro-op Queueも保持するデータの構造が違うと思われる。ただこうした差はマイクロコードRomまでで吸収されるはずで、Dispatchから下は差がないだろう。

実はそう考えると、FPU2がFMA256命令をサポートしない理由もなんとなくわかる。本来のFPUはSSEとNEONの両対応がメインで、そこに互換性を維持するためAVX256を追加した、という感じだからだ。

ARMは今年のHotChipsで、128bit単位で最大2048bitまでの幅を持つSIMDエンジンであるScalable Vector Extensionsという新しいSIMD命令を発表したが、これに対応することは考えていないと思われる。筋論から言えば、AMDはHPC用途にはPolarisやVEGAなどのGPGPUを使いたいところで、K12に長大なSIMDエンジンを搭載することは考えていないだろう。

以上のように、だいぶ強力なコアであることがあらためて確認できたのは非常に喜ばしいことで、年末の発表が待ち遠しいところだ。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ