約1年近く続けてきたスーパーコンピューターの系譜。その最後として今回はFPGAを解説したい。

古くはCCC(Cray Computer Corporation)の閉鎖後に設立されたSRC Computersが、FPGAをベースとした製品をリリースしていた(現在もしている)し、CRAYも一時期XD1をリリースしていた。

昨今はマイクロソフトがデータセンターでFPGAを使っていたという話もあり、実はデータセンター向けのニーズが徐々に増えつつある。このFPGAについては連載307回でさらっと解説しているが、もう少し細かく説明しよう。

あらゆる回路を構成できる反面

ICを複雑につなぐ必要がある

FPGAはField Programmable Gate Arrayの略である。“Field Programmable”が肝で、つまり製造後に内部のロジックを書き換え可能なゲートアレイという意味となる。もちろん、これでは意味がわかりにくいだろう。

そもそもデジタル回路はすべて0か1の2値で表現される、という話は連載237回で紹介した。

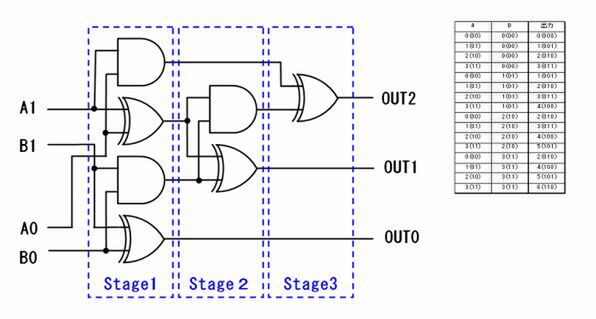

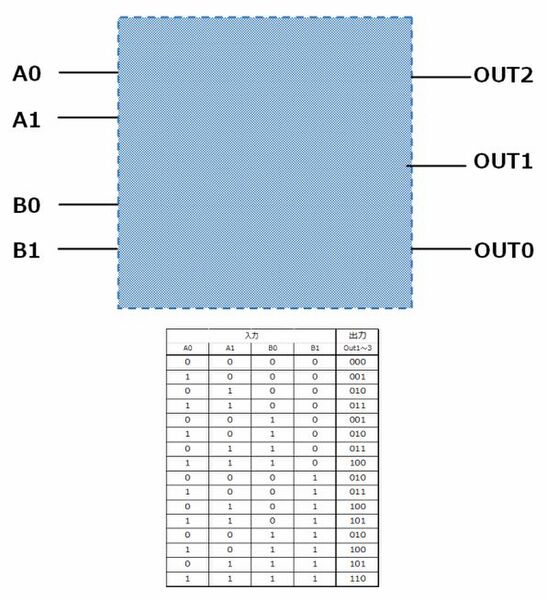

連載237回では2bitの加算器(Adder)回路を解説したが、全体を「入力が4bit(A0/A1/B0/B1)、出力が3bit(OUT 0/1/2)の箱」とみなすこともできる。

したがって、図2のように、4bitの入力と3bitの出力の組み合わせが図1とまったく同じ別の回路を構成すれば、それは図1の回路と置き換えて2bitの加算器(Adder)と称することができる。ここまでは普通の話だ。

当初、真空管やトランジスタベースだったデジタル回路は、TI(Texas Instruments)の7400シリーズや、その後継の標準ロジックICをベースに構成できるようになった。

この7400シリーズはものすごく多い(Wikipediaに一覧がある)ため、これを組み合わせれば複雑な回路も構成できる一方、標準ロジックに含まれていない回路を組みたい場合、標準ロジックICを複数個、複雑につなぐ必要があり、これが面倒だった。

そこで、回路を自由に構成できるICがほしい、という希望は昔から多くの人が抱いていた。これを最初に実現したのがPLD(Programmable Logic Device)である。

製品としてはMonolithic Memories, Inc.(1987年にAMDに買収され、その後Vantisとしてスピンアウト後、Lattice Semiconductorに買収された)がリリースしたPAL(Programmable Array Logic)が最初のものとなる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ