2週間空いてしまったが、スーパーコンピューターの話を続けよう。今回は再びアメリカに戻る。1984年、サンノゼでCydromeという会社が創立された。

創立メンバーはDavid Yen博士、Wei Yen博士、Ross A.Towle氏、、Arun Kumar氏、Bob R. Rau博士といった面々である。

ネタバレになるかもしれないが、これらの面々のその後の経歴を紹介しておくと、David W. Yen博士はSun Microsystemsの副社長やJuniper Networkの副社長、Ciscoの専務などを歴任。

Wei Yen博士はその後SGIの専務を勤めながら同時にArtXを創立、その後はいくつかの会社の取締役会に名前を連ねたり創立したりしつつ、現在はAcer Cloud Technologyを率いている。

Arun Kumar氏は、SGIのディレクターを経ていくつかの会社のCEO/CFOを勤め、現在はITA(International Trade Administration:アメリカ合衆国商務省国際貿易局)の次官補という役職に就かれている。

そしてCydra 5のチーフアーキテクトを勤めたBob R. Rau博士はHPの研究員となって2002年に逝去された。さて、このメンバーのその後の経歴に何かしら連想されるものがないだろうか? というのが今回のお題だ。

その話は後にするとして、このCydromeという会社は独自のアーキテクチャーのシステムであるCydra 5を開発した。まずはここから解説したい。

50~100万ドル程度で購入可能な

気軽に使えるシステム「Cydra 5」

Cydra 5の目的は、50~100万ドル程度で購入可能でありながら、1000~2000万ドルクラスのスーパーコンピューターの1/4~2/3程度の性能が期待できるシステムである。

彼らはこれを強調すべく、Cydra 5 Departmental Supercomputerと呼んでいた。Departmentalというのは部門の意味で、要するに組織全体で使うものではなく、部門ごとに導入して気軽(?)に使えるようなシステムを目指していたということだ。

もちろん、そんなシステムが簡単にできるわけもないので、さまざまなテクニックに加え、いくつかのトレードオフを考慮していた。

Cydra 5の元をたどると、米TRWのESL(Electromagnetic Systems Laboratory)が開発していたPolycyclic Architectureに基づくベクトルプロセッサーに行き着く。

一種のデータフロー・アーキテクチャー(データが来た順に処理を行なう仕組み)で、多くのデータフロー・アーキテクチャーと同じようにこれも非同期構成だったらしい。

Cydra 5は同期式のシステムなので、この点では異なるのだが、これに近い概念を実現するために複数種類のプロセッサーを混在するヘテロジニアス・マルチプロセッサーの構成を取った。

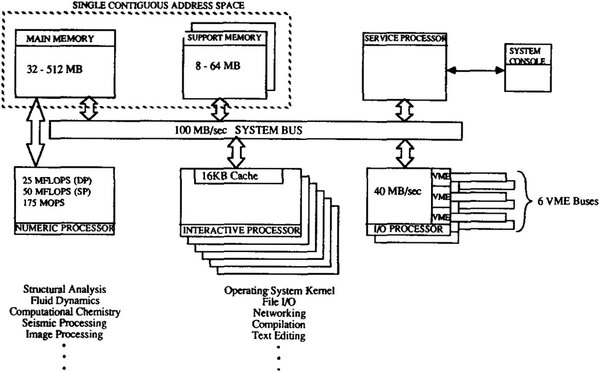

下図が全体の構成であるが、中核にあるのがインタラクティブ・プロセッサーで、ここが計算以外のほとんどの処理を担う。

※画像の出典はCydromeの“The Cydra 5 Departmental Supercomputer: Design Philosophies, Decisions and Trade-offs”(http://ieeexplore.ieee.org/xpl/login.jsp?tp=&arnumber=47160)。以下の資料も出典は同じ。

I/O向けにはI/O Processorが別に用意され、またシステム管理用にService Processorも搭載されるが、計算処理は別に用意されたNumerical Processorが担うという仕組みだ。

ここでトレードオフとして、Numeric Processor以外は、トータルで10MIPS程度の性能があれば良いと割り切り、比較的低速なプロセッサーを複数並べる構成とした。

ちなみに10MIPSという数値は、Numeric Processorが必要とするデータの読み書きなどをハンドリングするのに、この程度があればなんとかなるという試算だった模様だ。

1984年の時点ではまだ主要なRISCプロセッサーはあくまでペーパープラン、もしくは設計中ということで、唯一利用できる製品はMotorolaの16MHz駆動のMC68020であった。

資料には明示的には書かれていないが、どうもNumeric Processor以外はすべて16MHz駆動のMC68020で実装した模様だ。性能的には33MHzのMC68020で5.36MIPSという数字があるので、16MHzだとおよそこの半分になる。

そこで、MC68020を複数個搭載した。最低限4つあれば合計で10MIPSを超えるが、実際はもう少し多く実装したようだ。

→次のページヘ続く (演算性能を上げるために細かい並列性を高める)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ