Zenのクロックは3GHzと予想

2016年のComputexで公開か?

最後がAGUである。AVX命令の場合が一番クリティカルなのでこのケースで考えてみる。FMAC、つまり乗加算を同時に行なう以下のような演算をAVXで実行する場合だ。

Y=A×X+B

AとBが定数ならば、単にXを読み込んでYを書き出すだけで済むので、1サイクルあたり256ビット=32バイトというわけで、32バイト/サイクルのロードとストアーが同時に行なえれば理論上は間に合う。

もちろん、同じFMACでも例えば以下のように、XとYを読み込んでZを書き出すケースだとこれでは不足する。

Z=X×Y+B

インテルがHaswellでロードユニット×2+ストアーユニット×1という重厚な構成にした(関連リンク)のは、こうしたケースでもキャッシュへの帯域がボトルネックにならないようにという配慮である。

ただ先に書いたとおりAGUは2つしかないので、これを実現しようとするとAGUの帯域を64バイト/サイクルに増やさないとマッチしないことになるが、さすがにこれは考えにくい。現実問題としてそのあたりは割り切ったのだろうと想像される。

今回の推定図は、あくまでもZen用のパッチコメントからの情報と、Waldhauer氏との議論で出てきた内容を元に筆者が予想しているものなので、これが正確かどうかはフタをあけてみないと判断できない。

Waldhauer氏は、他にAMDの取得した特許情報などを元に自身の推定を補強しているが、筆者はそのあたりは今回採用していない。

いずれにせよ、すでにAMDはK12とZenをテープアウトしたことを第4四半期の電話会議で発表しており、製造に問題がなければ2016年のCOMPUTEXあたりのタイミングで動作するシリコンがお目見えするかもしれない。

最後に、Waldhauer氏は動作周波数として3.5~4GHzという数字を挙げておられるが、筆者はもう少し控えめな数字(~3GHz程度)ではないかと予想する。

これは利用すると思われるGlobalFoundriesの14nm LPE(LPPが間に合うかはタイミング的に微妙)、あるいはTSMCの16nm FinFET+が、3GHzを超えるとさすがに消費電力がバカにならないからだ。性能/電力比を重視すると、どうしてもプロセスに関してもあまり攻めた設定はしにくい。

そもそもTSMCにしてもGlobalFoundries(というよりSamsung)にしても、現在提供しているFinFETプロセスはいずれもモバイルSoC向けを主眼に置いたもので、ターゲットはせいぜい2.5GHz程度で、がんばっても3GHzというあたりだ。

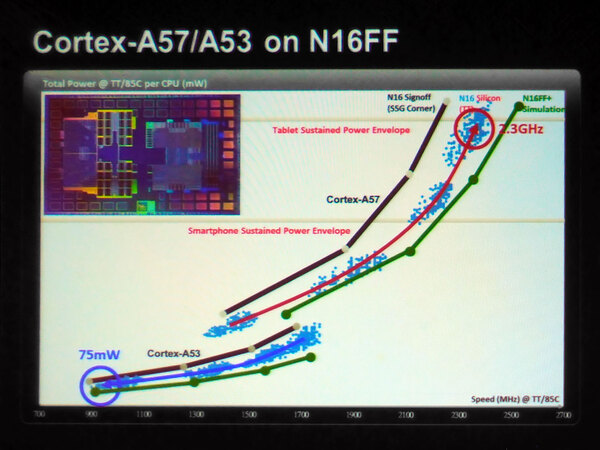

下の画像は2014年のARM TechConにおけるTSMCの資料だが、だいたい2GHzあたりから消費電力が急増しており、おそらく3GHzでCortex-A57を動作させると2Wでは効かないだろうし、4GHzあたりは想像もできない。

Cortex-A57が1コアでこれなので、Zenクラスを4GHzで動かすのは無理だと思われる。このあたりの事情はGlobalFoundriesもほとんど同じである。したがって筆者は最大で3GHzという予測を立てている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第876回

PC

このままではメモリーが燃える! HBM4/5世代に向けた電力供給の限界と、Samsungが示すパッケージ協調設計の解 -

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 - この連載の一覧へ