1EFlopsに向けた

性能/電力比の改善への取り組み

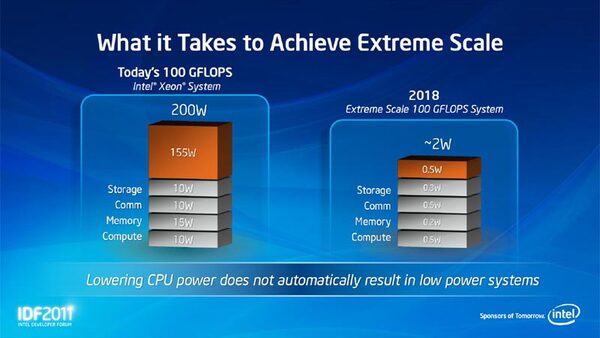

ラトナー氏の講演は、将来の「ExaScale」(エクサスケール)の話へと進んだ。ExaScaleというのは、2020年までに1EFlops(=1000PFlops)を目指すという開発プロジェクトである。このプロジェクトは単に性能だけではなく、今後10年で性能/電力比も現在に比べて、300倍も改善するという。

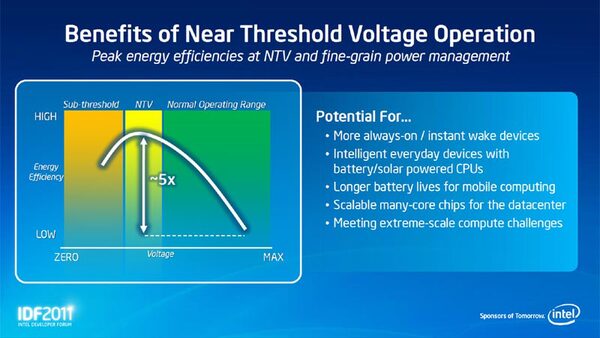

そのための取り組みのひとつとして、最初に紹介された内容が「NTV」(Near Threshold Voltage、限界しきい値電圧)で、これによりトランジスターの動作効率を最大5倍程度改善できるとしている。

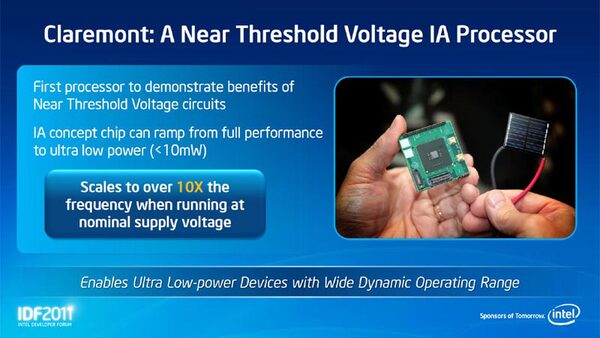

初日の基調講演に登場した謎の「太陽電池で動くCPU」であるが、これはNTVを応用して試作されたもので、10mW未満の消費電力で動作するという。コード名は「Claremont」。今回のデモでは、あくまでも従来比5倍程度の改善に留まるが、これは既存のCPUコアをそのまま使ったからで、新規にコアを設計すれば8~10倍が期待できる。

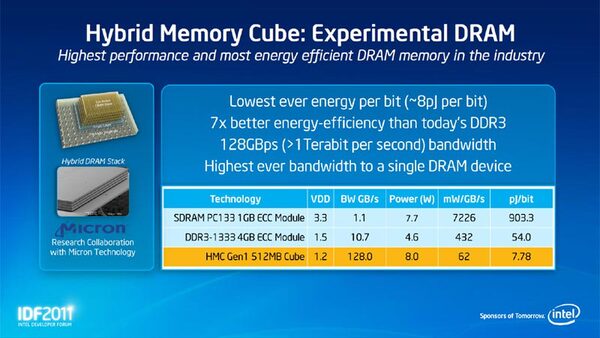

もうひとつの取り組みは、先ほども触れた「広帯域メモリー」である。今回インテルはメモリーベンダーのマイクロンと共同で、「HMC」(Hybrid Memory Cube)と呼ばれるものを発表した。これは4枚のDRAMをシリコン貫通端子を使って積み重ねたもので、8Wの消費電力で512MBのメモリーに128GB/秒(1Tbps)でアクセスできるという。デモでは実際に、120GB/秒程度のアクセス速度を示した。

ラトナー氏の基調講演の内容は以上である。今回は基調講演そのものが毎回1時間と短かったこともあってか、テーマをメニイコアに絞ってその将来性を説明するとともに、必要とする付帯技術を紹介するという流れであった。CTOであるラトナー氏の立場からすると、22nmで製造されるKnights Connerが立ち上がってくれるのが最優先の任務で、そのユーセージモデルや利点を、直接製品を使わずに紹介するという困難な任務を、うまく達成したのではないかと思う。

この連載の記事

-

第3回

PC

IDFでインテルが明らかにした耐久性の高いSSD -

第2回

PC

2012年のノートPCは待機時間・消費電力がさらに減る -

第1回

PC

IDF初日の基調講演で注目はAndroidのAtomへの最適化 - この連載の一覧へ