IDF 2011レポートの最終回は、15日(現地時間)に行なわれたインテル上級副社長兼CTOのジャスティン・ラトナー(Justin Rattner)氏による、インテルのメニイコアプロセッサーに関する基調講演をまとめてみた。

Larrabee改めIntel MICアーキテクチャー

いよいよ製品登場?

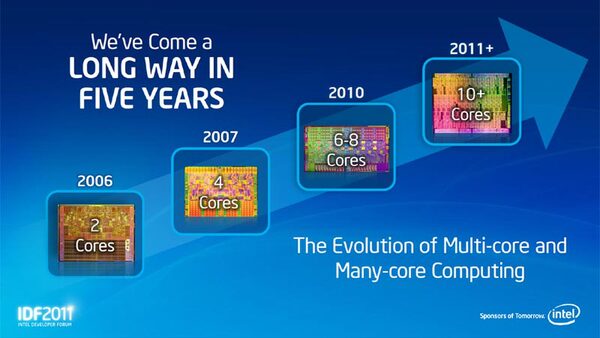

ラトナー氏はまず、ここ5年でのプロセッサー開発の動向を簡単に振り返りつつ、より多くのCPUコアが半導体ダイに搭載されるようになってきた昨今を紹介して、「今後はヘテロジニアス(異種混合)構成が登場する。ただし、それは単にGPUだけを指すのではない」として、「Intel MIC(Many Integrated Core)アーキテクチャー」について説明した。

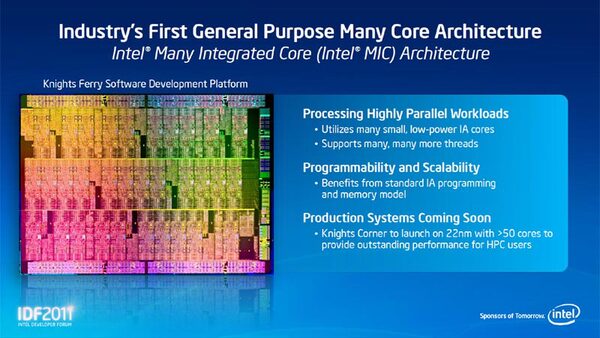

Intel MICアーキテクチャーの最初のチップである「Knights Ferry」は、ようするにインテルが「Larrabee」のコード名で開発してきたプロセッサーである。しかし、「性能などが十分ではない」として製品化を見送られており、あくまでソフトウェア開発者向けの開発プラットフォームとしてのみ提供していた。これに続く「Knights Conner」が、Intel MICアーキテクチャー最初の製品となる。

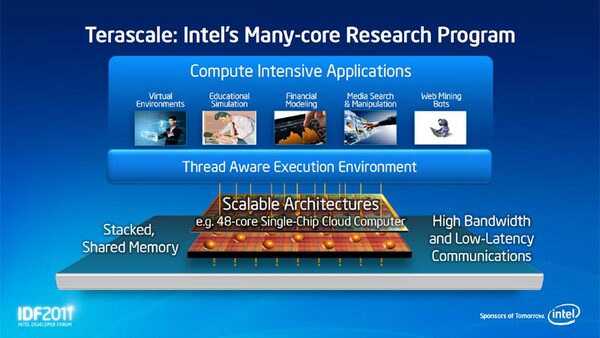

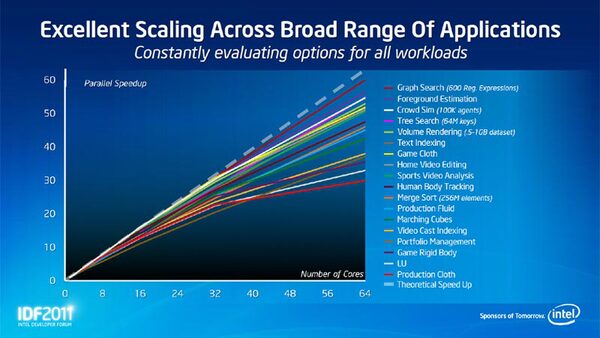

単にCPUコアを集積しただけでは、性能が出るわけもない。ここで必要なのは、広帯域のメモリーと、複数コアで性能を出しやすいアプリケーションだ。

この連載の記事

-

第3回

PC

IDFでインテルが明らかにした耐久性の高いSSD -

第2回

PC

2012年のノートPCは待機時間・消費電力がさらに減る -

第1回

PC

IDF初日の基調講演で注目はAndroidのAtomへの最適化 - この連載の一覧へ