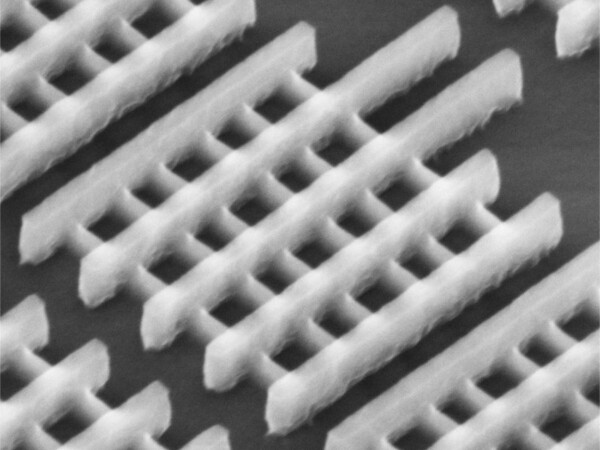

メモリー編の途中であるが今回は予定を変更して、5月4日(現地時間)にインテルが発表した、22nmプロセスの「三次元トライゲート(Tri-Gate)・トランジスター」について解説したい。とは言っても、いきなり「トライゲートとはなんぞや」の話をしてもわけがわからないと思う。まずは基礎となるトランジスター(FET、電界効果トランジスター)の構造から説明しよう。

トランジスターの微細化と高速化の理屈をおさらい

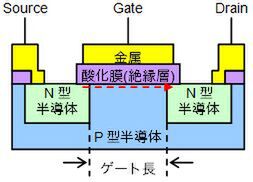

図1は回路図に出てくるFETの構造である。これは「NMOS型」というタイプのFETであるが、この動作原理をごく単純化して説明すると、ソース(Source)とゲート(Gate)の間の電圧を変化させると、これに連動する形でソース/ドレイン(Drain)間の電流が変化する、というものだ。つまり電圧を変化させることで、ソースからドレインへの電流をオン/オフできるという仕組みである。

図1 電界効果トランジスターの構造

このNMOS型のFETの構造を、側面から断面図の形で示したのが図2である。ソース/ゲート間の電圧を変化させると、それにともなって電流が赤い破線のように、ソースからドレインへと流れるという仕組みだ。この基本的な構造そのものは、初期のCMOSから最新のトライゲートまでまったく同じと考えていい。

図2 トランジスターの側面図

ところが、半導体製造技術の進化によってトランジスターの構造が微細化していった結果、多くの問題が出てくるようになった。初期の数μmサイズの製造プロセスから180nmあたりまでは、プロセスを微細化するほどトランジスターは高速に動作して消費電力が減っていた。

物理的なサイズも小さくなるから、同じ回路ならば半分のダイサイズで製品が作れるし、ダイサイズを同じにすれば2倍のトランジスターが利用できるから、その分高機能や高性能にできる。180nmあたりまでは、単にプロセスを微細化するだけで皆がハッピーになれた。この傾向が怪しくなるのは、130nmあたりからだ。そして90nmプロセスでは、微細化にともなう副作用が大きな問題として出てくるようになった。

そもそも、なぜ微細化すると高速化や省電力化できるのか? それは微細化にともないゲート長の間隔が狭まったことに起因する。ゲート長というのは、ソースとドレインの2つのN型半導体の間の距離(NMOSの場合)のことだが、これが長いと当然ながら抵抗が大きいので、高い電圧をかけないと電流が流れないし、距離が長いから伝達遅延も増える。

逆に距離が短くなれば抵抗が減るので、それほど電圧をかけなくても電流が流れるようになる(よって消費電力も減る)。伝達遅延は距離に比例するから、ゲート長を縮めれば遅延も減り、結果として高速で動作する。

このあたりは、水道管の蛇口をイメージするとわかりやすい。昔は凄く大きな蛇口だったのでパッキングも分厚く、蛇口を目一杯捻らないと水が出なかった。そこで蛇口を小型化して、かつパッキングも薄くしたことで、蛇口をちょっと捻ると水が出てくるようになった、というイメージである。ところが、ある限度を超えて小型化した結果、今度は常に水が漏れる状態になってしまったわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 - この連載の一覧へ