微細化による高速化と省電力化を妨げる

リーク電流の問題

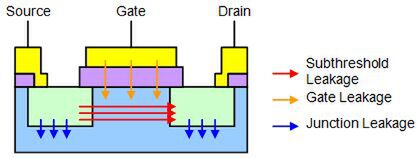

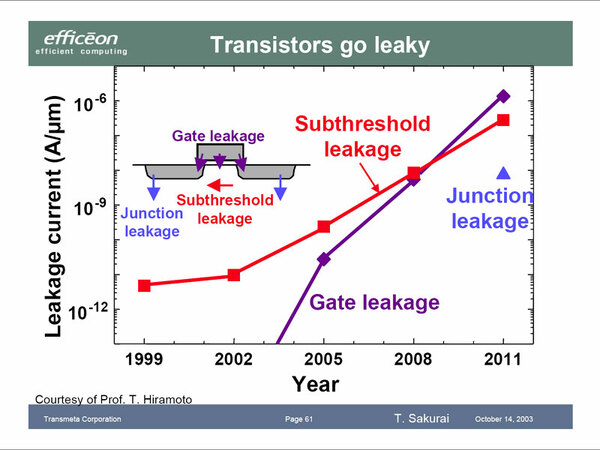

トランジスターの場合、まず最初に出てきたのが「Subthreshold Leakage」(サブスレッショルドリーク電流)の問題である。ついで「Gate Leakage」(ゲートリーク電流)の問題が現われ、最後に「Junction Leakage」(接合リーク電流)が問題となってきた(図3)。

サブスレッショルドリーク電流というのは、ようするに「パッキングを薄くしすぎたので、蛇口を閉めても水が駄々漏れになる」状態のようなものだ。ゲートリーク電流は「蛇口を閉めたら、蛇口のノブあたりから水が漏れ出してしまった」状態。接合リーク電流は「蛇口の手前の水道管で水が漏れ出してしまう」状態になる。

実のところ、こうした問題の登場は昔から予想されていた。下のスライドはこれを示した予測である。180nm世代ではそれほど大きな問題になっていないサブスレッショルドリーク電流が、65nm世代ではおおむねね1000倍近くに跳ね上がっている。さらに45nm世代では、加えてゲートリーク電流も同程度に増えると予測されていた。縦軸が対数グラフである点に注意されたい。

インテルのプロセスの場合、65nm世代どころか90nm世代でも無視できないサブスレッショルドリーク電流が発生した。これがPrescottコアPentium 4の息の根を止める原動力(?)になったのは、連載61回で解説したとおりである。

歪シリコンにHigh-Kメタルゲート

リーク電流対策に用いられた手法

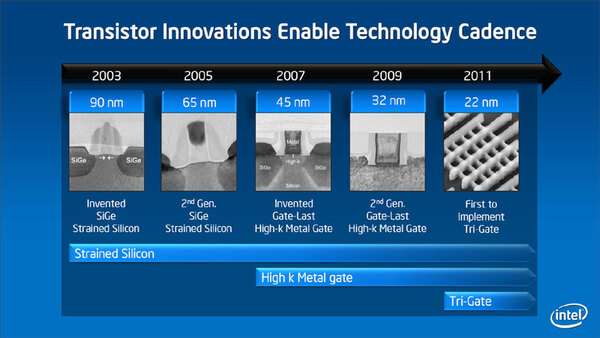

そこで、こうしたリーク対策をどこまで施すかが、トランジスター開発の主要なテーマになり始めた。下のスライドは90nm世代以降のインテルのプロセスをまとめたものだが、例えば90nmと65nmで利用された歪シリコン(Strained Silicon)は、半導体に「物理的に歪ませる」ことで、電荷の移動速度を上げる技法であった。これによって、歪シリコンを使わない場合よりも高速にトランジスターを動作させられるようになったし、これを逆にサブスレッショルドリーク電流を減らす方向に使うことで、性能を確保しながらリーク電流を減らすことに成功している。

同様に、45nm世代で導入された「HKMG」(High-K/Metal ゲート)は、ゲートリーク電流削減に貢献する手法だ。こちらは誘電率の高い(High-K)材料をゲートに配することで、絶縁膜の厚みを減らさずにスイッチング速度を確保する手法である。それまでは、プロセスの微細化にともなってゲートの絶縁膜もどんどん薄くなり、ついに65nm世代では原子3つ分というところまで来てしまった。ここまで薄くなれば、電流が漏れても致し方ないところである。

High-K材料を使うと、この原子3つ分の場合と同じ程度のスイッチング速度を、もっと厚い(=電流が漏れにくい)絶縁膜経由で実現できる。ただし、このHigh-K材料は相性問題が強く出やすく、これまで電極(図2、3の黄色い部分)に使ってきたポリシリコンとの親和性が悪いという問題があった。そこで、ポリシリコンとHigh-K材料の間に金属を挟み、直接両者が接触しないようにするのがメタルゲートというわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ