前回までに、CPUには複数のキャッシュが搭載されていることを説明した。今回はそのキャッシュをどう制御するか、という話をしよう。

3階層のキャッシュのどこにデータを置くか?

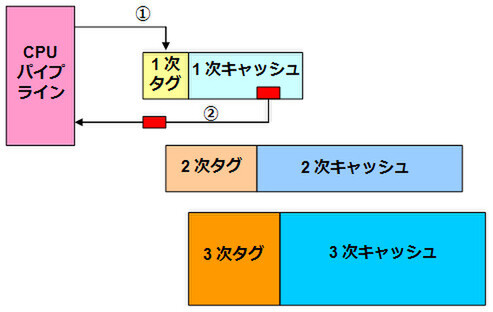

例えば図1のように、1次~3次までキャッシュを持つCPUを考えてみる。ここでCPUがデータ(命令でもいい)のフェッチを掛けた場合、まずは1次キャッシュのタグを検索する(図1-①)。ここで見つかれば問題なく、単に1次キャッシュからそのデータを引っ張ってくる(図1-②)だけでいい。問題は1次キャッシュにデータがなかった場合(キャッシュミス)である。

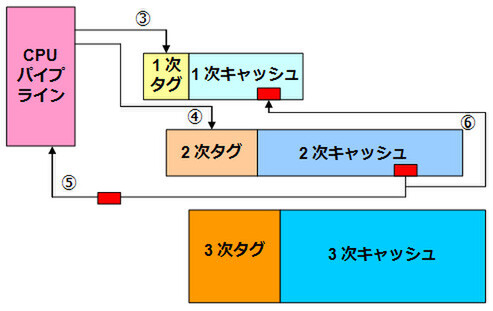

図2は、2次キャッシュでヒットした場合だ。まず1次タグを参照し(図2-③)、ここにないことがわかったら、次は2次タグを参照する(図2-④)。2次タグで発見したら、2次キャッシュからデータをフェッチする(図2-⑤)とともに、1次キャッシュにもキャッシュフィル(データのコピー)を行なう(図2-⑥)。

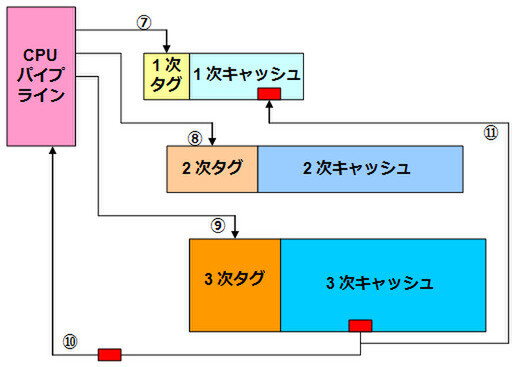

これは1次ミス/2次ミス/3次ヒットの場合でも同じである(図3)。今度はまず1次タグ(図3-⑦)/2次タグ(図3-⑧)/3次タグ(図3-⑨)と順に参照して、3次タグで発見したらそこからフェッチする(図3-⑩)とともに、1次キャッシュへのフィルも行なう(図3-⑪)。

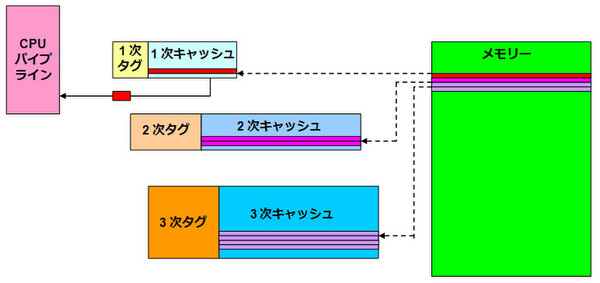

問題は、この1次/2次/3次キャッシュに、何がどのタイミングで入るのか、である。通常のCPUでは、「Implicit Prefetch」(暗黙のプリフェッチ)という機構が利用される。例えば図4のような仕組みだ。

CPUがあるメモリーアドレスのフェッチを要求し、1次/2次/3次とすべてのキャッシュがヒットしなかったケースを考えてみる。この場合、CPUはそのメモリーアドレスを指定してメモリーアクセスするわけだが、通常この際には、1ライン分のメモリーを取得する(取得したと思っている)。しかし、実際には指定したアドレスから7ライン分のメモリーを取得し、1次キャッシュには目的のラインを、2次キャッシュには目的のラインに続く2ライン、3次キャッシュにはさらに続く4ラインを同時に格納するといったメモリーの取り込み方をする。

これにより、例えば1次キャッシュに取り込んだラインを使い切っても、その次の領域は2次キャッシュに、さらにこれに続く領域は3次キャッシュにすでに取り込まれている。だから、最低限のレイテンシーで7ライン分までアクセスできることになる。

ちなみに、これはあくまでも概念であって、実際の実装方法は異なったものである。例えばインテルの場合、「Pentium M」「Pentium 4」までで利用された方法と、Coreマイクロアーキテクチャーで採用された方法では、特に2次/3次キャッシュに対するキャッシュフィルの方法が若干異なる。同じメーカーのCPUでも、アーキテクチャーによってこのあたりの方法論は変わることがある。

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ