これは別の観点からも説明できる。前回説明したとおり、キャッシュをアクセスするためには「それがキャッシュのどこにあるか」を毎回確認する必要がある。そのためにタグRAMにアクセスするわけだが、キャッシュの容量が大きくなると、タグへのアクセスに当然余分に時間が掛かることになる。

もちろん「セットアソシエイティブ」を使うことで、ある程度時間の増加を抑えることはできるが、Penrynコア(Core 2 Duo)の2次キャッシュのように「24ウェイ」もの構成になると、どうやっても所要時間はそれなりにかからざるをえない。そうなるとキャッシュアクセスのレイテンシーが悪化することになり、これはそのままCPU性能の足かせになりかねない。

こうしたこともあり、キャッシュも多段階構成にすることがリーズナブルであると判断された。つまり、本当に最小のレイテンシーでアクセスできるものを1次(Level 1)キャッシュとして小容量に留める。もう少しレイテンシーは大きくなるが、やや大容量のものを2次(Level 2)キャッシュ。さらにレイテンシーが大きくなるが、もっと大容量のものを3次(Level 3)キャッシュとして、それぞれ実装するというものだ。

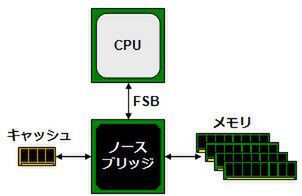

「Katmai」(初代Pentium III)やK7/K75コアAthlonの頃までは、物理的に大容量のキャッシュはCPUダイに搭載できないという問題があった(ダイサイズが大きくなりすぎ、原価が高くなり歩留まりも一気に悪化する)。そのため、まずPentiumの時代までは、図6のように2次キャッシュをノースブリッジ側に置き、キャッシュ制御そのものもノースブリッジが行なっていた。

図6 Pentium時代までの2次キャッシュの実装例

この時代のキャッシュとしては、「PBSRAM」(Pipeline Burst SRAM)が利用されていた。速度はFSBと同じ程度で、CPU内部のキャッシュに比べると数倍遅いが、最大2MB程度のSRAMモジュールが利用できた。メモリーと比べた場合、ピーク性能では大差ないが、SRAMのために理論上1クロックでアクセスできるため、レイテンシー短縮の観点でメモリーを使うよりも高速だった。

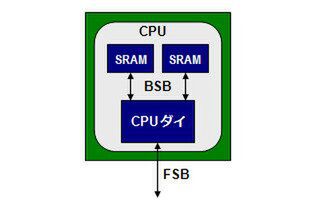

ただし、これではFSBの速度で2次キャッシュの速度が決まってしまう。そこで高速化のため、図7のようにCPUパッケージの内部にSRAM(PBSRAM)を搭載する形に進化した。ここではCPUダイとSRAMはBSB(Back Side Bus)というキャッシュ専用バスで接続され、キャッシュの制御もCPU側に移っている。

図7 Pentium Proの2次キャッシュの実装例

最初にこれを実装したのはPentium Proだが、「MCM」(Multi-Chip Module)という形で実装したところ、当時の技術では実装コストが非常に高くなりすぎてしまった。そのためPentium II/IIIやAthlonでは、大きなモジュール基板の上にCPUのダイと汎用のPBSRAMチップを載せる形で、低価格化を図っている。

ちなみにPentium Proでは、2次キャッシュの速度はCPUコアと一緒であったが、Pentium II/IIIではCPUの速度が高速化しすぎて汎用のPBSRAMチップでは追いつかなくなったため、CPUの速度の何分の1で動作する形に切り替わった。当初は「2分の1」だったが、K75では「5分の2」や「3分の1」など、いろいろ工夫をこらして何とか追いついていたものだ。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ