x86の問題を解消する、

命令の並べ替えとレジスタリネーミング

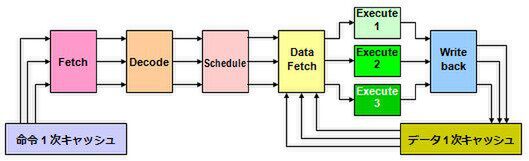

この問題は、そもそもx86命令が、スーパースカラーを前提としたような命令セットになってないことによる。スーパースカラーの場合、うまく命令を並び替えて、なるべく同時に複数の命令を実行できるようにすることが必要になるからだ。そのため、本格的なスーパースカラーの場合、実行に入る前にスケジューラーが設けられ、ここで命令の並び替えを行なう。

図3 Decodeの次にスケジューラーを実装したCPUのステージ構成

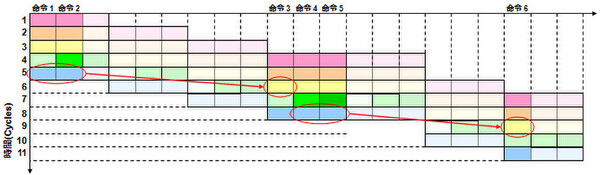

命令の並び替えとは何か? といえば、例えば以下のような命令が並ぶとする。これを従来のパイプラインで実行すると、図4のようになる。

- 命令1 R1=Data1

- 命令2 R2=Data2

- 命令3 R3=R1+R2

- 命令4 R4=Data3

- 命令5 R5=Data4

- 命令6 R6=R4+R5

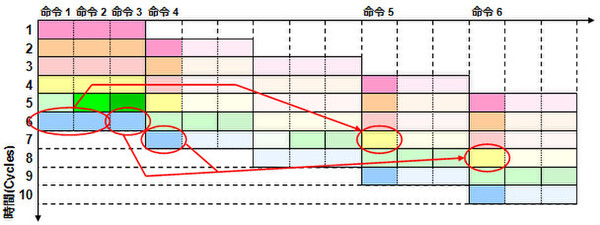

ところが命令を以下のように並び替えると、命令1~4までを一気に実行できるため、命令5の開始のタイミングは一緒でも、命令6の開始を1サイクル早くできる(図5)。

- 命令1 R1=Data1

- 命令2 R2=Data2

- 命令3 R4=Data3

- 命令4 R5=Data4

- 命令5 R3=R1+R2

- 命令6 R6=R4+R5

この「命令の並べ替え」を行なうのが、図3で追加されたスケジューラーの処理である。なるべく同時に複数の命令を実行できるように、うまく並べ替えることで、命令の実行効率を高めようという手法だ。これに絡む技術が「レジスタリネーミング」である。例えば、命令が以下のような場合は並べ替えできない。

- 命令1 R1=Data1

- 命令2 R2=Data2

- 命令3 R3=R1+R2

- 命令4 R1=Data3

- 命令5 R2=Data4

- 命令6 R4=R1+R2

理由はR1、R2というレジスターを使いまわしていることに起因しているのだが、実はx86の場合、こうした問題が起きることが多い。x86では8つの汎用レジスターが利用できることになっているが、実際は非常に制約が多いため、実際に使えるのは3つ程度となっており、これでなんとかやりくりすることが多い※1。

※1 これをカバーするために、スタックと呼ばれるデータの一時保管構造を多用して、それがまた性能低下の一因になるのだが、また別の機会に説明する。

そこで、内部にたくさんの汎用レジスターを、プログラムからは見えない形で用意しておき、これを適時書き換えて使うというのがレジスタリネーミングである。上の例の場合、以下のように内部でこっそり書き換えてしまう。これでもう、レジスターの使いまわしで制約をうけることはなくなるわけだ。

- 命令1 R101=Data1

- 命令2 R102=Data2

- 命令3 R3=R101+R102

- 命令4 R103=Data3

- 命令5 R104=Data4

- 命令6 R4=R103+R104

ただし、ここまでやっても最初の問題である「依存関係の解消」は、そう簡単に成し遂げられるものではない、というのがスーパースカラーの最大の問題である。と言うのも、スケジューラーによる命令の並び替えも万能ではなく、特に同時処理する命令数が増えれば増えるほど、この並べ替えの難易度が増すためだ。

実際、スーパースケーラーを最初に実装したx86は、インテルのPentiumとCyrixのM1※2だが、どちらも2命令のスーパースケーラー程度だった。それ以上同時発行命令数を増やすには回路規模的に複雑すぎて、当時のプロセス技術では不可能だったこともあるが、単純にスーパースケーラだけで3命令処理を行なっても(依存関係解消が難しいために)性能が上がらない、という問題があったことも事実だ。

※2 当初の計画では、CyrixのM1の方が先に実装して登場のはずだったが、開発の遅れからPentiumが先行してリリースされた(関連記事)。

これを解決したのは、次回説明するアウトオブオーダーや、その次に説明するRISC風命令への変換などの技術で、これらを組み合わせることにより大幅に性能を引き上げることが可能になった。

★

ちなみに、ここまでは複数の均一な実行ユニットが並んでいるかのように説明したが、当然このあたりの実装は製品によって異なる。「Cyrix MII」の場合は、ほぼ同じ命令を処理できる実行ユニット×2の構成だった。一方でPentiumの場合、「U Pipe」と「V Pipe」という2つのユニットが用意され、すべての命令を処理できるのはU Pipeのみ。V Pipeはよく使われるシンプルな命令のみを処理できるという構成になっていた。こうした構成は、例えばVIAの「Isaiah」こと「VIA Nano」プロセッサーでも利用されている。

x86以外に目を向けると、例えば「MIPS32 74K」というプロセッサーは、2本の演算パイプラインを搭載したスーパースカラー(アウトオブオーダーは搭載しない)構成だが、片方はALU(整数演算)のみ、片方はAGEN(アドレス生成)のみ、という極めて割り切った構成になっている。必ずしもスーパースカラーにはアウトオブオーダーは必要ないという例とも言えるが、x86の命令の複雑さが、やはりアウトオブオーダーや命令変換を必要とせざるをえない、という面はあるだろう。

次回はスーパースカラーと対になって語られるアウトオブオーダーについて解説したい。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ