CPUアーキテクチャーの進化

CPU高速化の常套手段 パイプライン処理の基本 【その1】

2010年09月06日 12時00分更新

パイプライン処理の基本

ステージごとに次々と処理させる

以上の基礎知識を踏まえた上で、もう少しCPU内部の話をする。一般にCPUの場合、行なう処理は次の5段階(ステージと呼ぶ)からなる。

- Fetch

- 次に処理すべき命令を、メモリーやキャッシュから取得する。

- Decode

- 取得した命令を解釈し、どんな処理を実行すべきかを決定する。

- Data Fetch

- 必要なら、処理に必要なデータを取り込む。

- Execute

- 処理する。

- Writeback

- 処理結果を出力。

古いCPUでは、DecodeとData Fetchが一緒になって4ステージとか、ExecuteとWritebackを一緒にして3ステージとか、FetchとDecodeも一緒にして2ステージとか、いくらでも簡単にはできるのだが、機能で分割すればおおむねこの5ステージとなる。

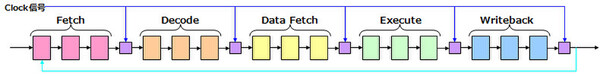

そしてこれらを実装する場合、内部回路は大雑把に図4のようになる。上の5つのステージはそれぞれ、複数の回路をつなげる形で実装されている。基本的には、Writebackの最終処理が終わったら、それをトリガーに次の命令のFetchを開始するような仕組みだ。

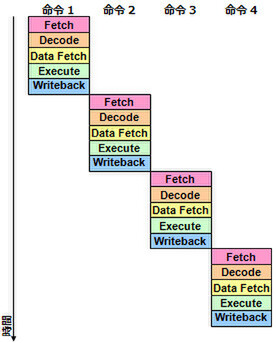

そして図4の場合、どのように命令が処理されてゆくかを示したのが図5である。ここではとりあえず、5つのステージがいずれも同じ時間で処理できるという前提にしているが、仮に1ステージ1クロックで処理できるとしても、1命令あたり5クロックを要することになる。図のように4命令実行なら、20クロック必要になる計算だ。

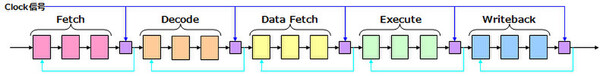

これを「もう少し高速化できないか?」ということで考えられたのが、パイプライン処理である。基本的な構造は変わらないが、これまでは「Writebackの出力が終わったら次のFetchを開始する」だったのが、「各ステージごとに、処理が終わったら次の命令の処理を始める」形に変更されている(図6)。

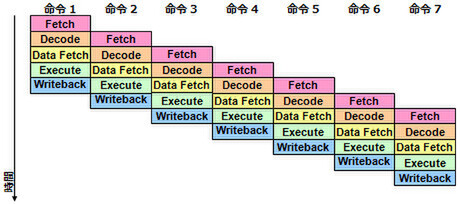

これを実行した場合、処理の進み方は図7のようになる。

各々のステージに要する時間は変わらないが、各ステージが常に処理を行なっているため、実質的な処理能力が(この図の場合)5倍になっているわけだ。こうした形で、常にCPUの内部回路全体が動作するようにしたものが、パイプラインと呼ばれる高速手法である。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ