CPUアーキテクチャーの進化

CPU高速化の常套手段 パイプライン処理の基本 【その1】

2010年09月06日 12時00分更新

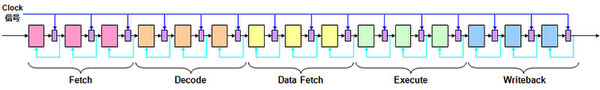

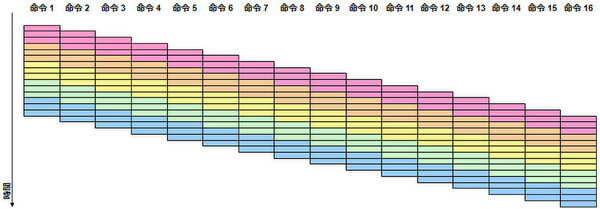

これをもっと高速化したい、という場合にはさらにパイプラインのステージを細分化することもある。図6では各ステージが3つの回路で構成されていたが、これを全部ばらばらにして、細かくラッチを入れた図8のような回路にした場合、動作周波数をさらに高速化できる(図9)。

これなら各々の処理に起因する遅れはさらに少ないから、ラッチのタイミングをもっと高速にしても十分間に合う。その分クロックの速度を引き上げられるというわけだ。こうした細分化したパイプライン構造を、「Super Pipelinging」(スーパーパイプライニング)、あるいは「Hyper Pipelining」と呼ぶ。

もっとも、こうしたパイプラインの増加は2つのデメリットがある。ひとつはパイプラインストールやパイプラインハザードなど、予想外の事態によりパイプライン処理が止まったり、やり直しになったりした場合、その影響が非常に大きいことだ。

もうひとつは、ラッチの数そのものが大幅に増えたことによる、消費電力の増大である。Pentium 4のNetburst Architectureの場合、前者は設計段階から想定されており、これを補うための仕組みが用意されていたが、後者に対する備えが甘かった。これが結果的に消費電力の増大や過大な発熱につながり、最終的には製品寿命を縮めることになってしまった。

ということで次回はパイプライン処理の問題とその対策を解説したい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ