CPUアーキテクチャーの進化

CPU高速化の常套手段 パイプライン処理の基本 【その1】

2010年09月06日 12時00分更新

これを補正するために登場するのが、ラッチ回路である(図3)。ラッチ回路というのはようするに、図1のSRAMそのものであり、「入力された値を保持し続ける」機能を持つ。

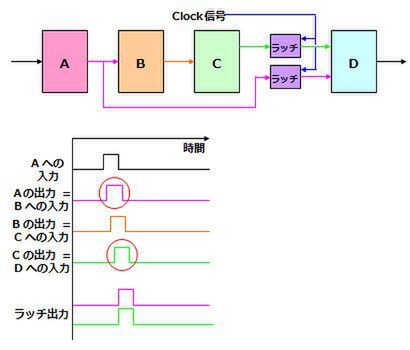

図3 図2にラッチ回路を加えた状態

先の例の場合だと、Dに入力される2つの信号にラッチを挟み込むことで、2つの信号が同じタイミングで出力されるようになる。このタイミングを決めるために使われているのが、いわゆるクロック信号である。つまりCPUの動作周波数とか言われているものは、実際には内部のラッチの動作タイミングを決定しているわけだ。

「動作周波数を上げると、その分トランジスターが高速に動く」と勘違いしている(実際ラッチ回路の内部に関してはそうなのだが)人もいるかもしれないが、図3で言えば、A~Dの回路にクロック信号は供給されていない。これらの回路内部のゲート回路やその中のトランジスターは、クロック信号とは無関係に動作する。

こうした形で、複数の回路の間にラッチ回路を挟み、そこに外部からクロック信号を入れる方式を、一般に「同期回路」と呼ぶ。最終的にはラッチ回路により、クロックのタイミングに同期して動作が進行するからだ。

同期回路があるということは、もちろん「非同期回路」もある。こちらはラッチを省く形で実装される。ぶっちゃけた話、CPUの消費電力の大きな部分はこのラッチ回路が占めており、これを省けば大幅な消費電力削減が可能となる。また図2と図3を見比べればわかるとおり、ラッチ回路は機能としては「信号を遅れさせる」ことになり、これは広い意味で性能低下の要素となる。

にも関わらず、非同期回路で製造されたCPUというのは、x86では皆無であり、もっと広い範囲で見てもARMとマンチェスター大学が共同で研究開発をした「Amulet」シリーズや、Philips(現NXP Semiconductor)の事業会社であったHandshake Solutions社の「ARM996HS」といったあたりのみ。製品化されたもので筆者が唯一知っているのは、シャープの「DDMP」(Data-Driven Media Processor)くらいしかない。

なぜかといえば単純な話で、ラッチなしではタイミング設計が極度に難しくなるからだ。実際、100ゲート程度の回路であっても、ラッチ無しで設計するのはかなり難しい。10000ゲートを越えると、CADなどでもかなり設計は困難になるだろう。タイミングのずれ方は一意に決まるとは限らない。特に昨今のように、プロセスの微細化にともなってトランジスターの動作特性のバラつきが大きくなっている状況では、相当マージンを多く取らないとまともに動くものは作れない。そうなると、むしろラッチを入れたほうが安定するし、設計も遥かに簡単だからだ。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ