インテル(株)は13日、都内でエンタープライズ市場向け戦略の説明会を開催、その中で4way以上のマルチプロセッサーサーバーに対応した『インテルXeonプロセッサMP』1.40/1.50/1.60GHz版を発表した。同日量産出荷開始で、1000個ロット時の価格は順に15万8660円、26万6900円、49万7680円。

|

|---|

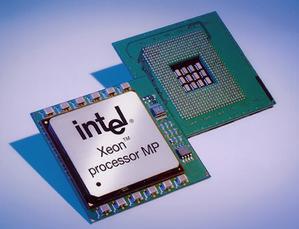

| 『インテルXeonプロセッサMP』 |

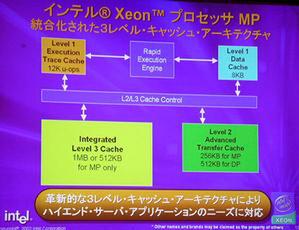

XeonプロセッサMP(以下Xeon MP)は0.18μmプロセス技術で製造され、8KB(データキャッシュ)と12KB(命令キャッシュ)の1次キャッシュ、256KBの2次キャッシュ、512KB(Xeon MP-1.40/1.50GHz)または1MB(Xeon MP-1.60GHz)の3次キャッシュをプロセッサーコア上に統合して搭載している。Pentium 4と同じNetBurstマイクロアーキテクチャを採用し、システムバスは400MHz、ストリーミングSIMD拡張命令2(SSE2)をサポートする。

|

|---|

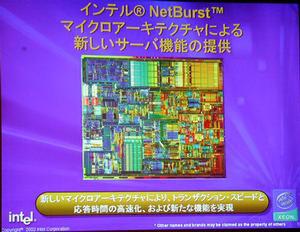

| Xeon MPのダイ画像 |

|

|---|

| Xeon MPのキャッシュ構造 |

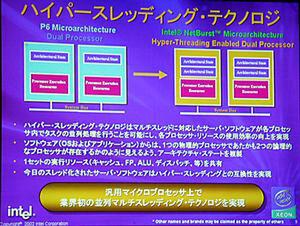

また2月26日に発表したワークステーション/サーバー用(デュアルプロセッサーまで対応)の『インテルXeonプロセッサ』1.80/2/2.20GHz版と同様、物理的には1つのプロセッサーだが、OSやアプリケーションからは2つのプロセッサーが存在するように見え、ソフトウェアがマルチスレッドに対応していれば、1つのプロセッサー内でタスクの並列処理が可能となる“HyperThreadingテクノロジ”を備えている。物理的に2つのプロセッサー(HyperThreading非対応)で構成するシステムにおいては、1つの場合と比べ60~80%程度性能が向上するが、HyperThreading対応の1プロセッサーのシステムではキャッシュメモリーや演算ユニットを共有する形となるため、約30%の性能向上にとどまる。

|

|---|

| HyperThreadingテクノロジの概要 |

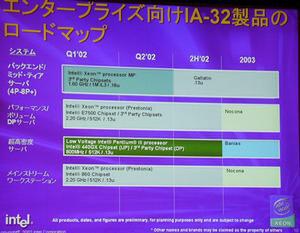

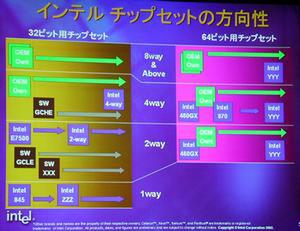

説明会においてインテルが示したIA-32製品のロードマップによると、2002年後半には、0.13μmプロセス技術を使い、3次キャッシュ容量を倍増させたXeon MP(コードネーム“Gallatin(ガラティン)”)を投入、デュアルプロセッサーまでのXeon後継としては2003年に“Nocona(ノコナ)”を投入するとしている。また、チップセットに関して、現在は各サーバーメーカーや米Server Works社の製品に頼っている4way以上のマルチプロセッシングに対応したチップセットを投入する方針であるという。ただし、投入の時期については明らかにしなかった。

|

|---|

| エンタープライズ向けプロセッサーのロードマップ。超高密度サーバー(Bladeサーバー)向けには“Banias”を使うという |

|

|---|

| チップセットの今後の投入方針(時間軸は明らかではない) |

|

|---|

| “McKinley” |

|

|---|

| Itaniumプロセッサーファミリーのロードマップ |