インターコネクト問題は光インターコネクトで解決できる

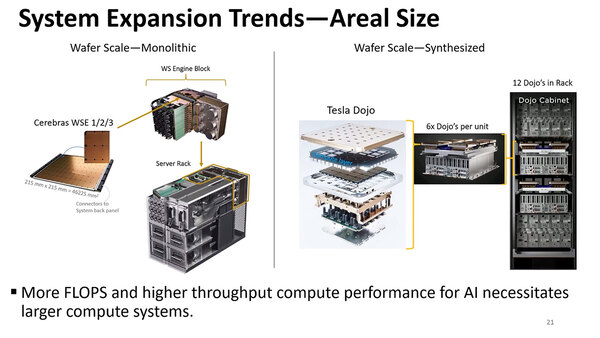

最後がシステムインテグレーションの話である。現状CelebrasのWSEなりTeslaのDojoなりが、製造できる最大のチップということになるが、これでもまだ性能が足りない以上、当然これを複数利用したシステムを構築することになる。

Wafer Scaleのプロセッサーであっても1つでは能力に限界があるので、複数チップをまとめてシャーシに収め、そのシャーシを複数台ラックに収め、そのラックを複数本束ねるという構成から逃げることはできない

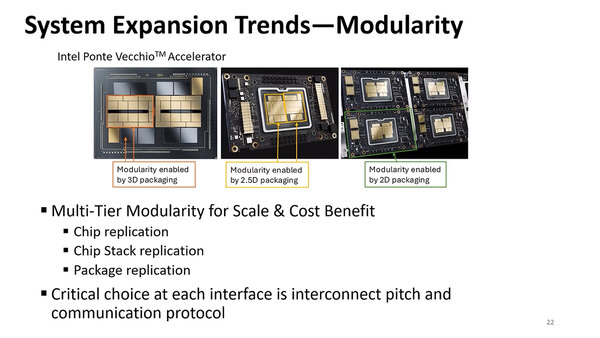

そういうケースでは、コストの面からモジュラリティを利用するのが得策というのが現在のトレンド、というのはMI300Xが一番適切な気がする。

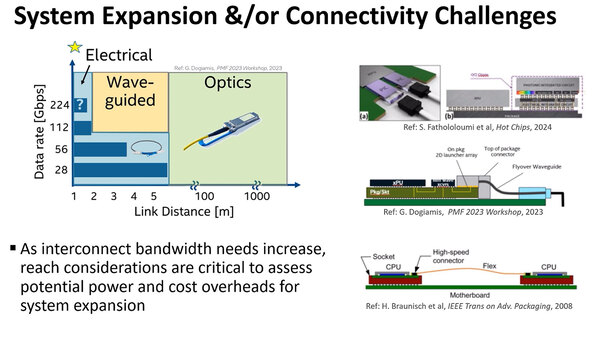

ただモジュラリティを追求しようとすると、またもやインターコネクトの問題が再現することになる。これに関する解の1つが、連載801回でも説明した光インターコネクトである。

電気信号は信号速度的にレーンあたり112Gbpsあたりが現在の技術では限界で、224Gbpsは短い距離ならなんとかという感じで、しかも消費電力が大きい。光インターコネクトはOCI/EICを別に設ける必要があるが、信号伝達に要する消費電力そのものは非常に小さいし、WDMを使えば信号速度も高くできる

チップレット同士の接続にはやや大げさすぎるが、モジュール同士、あるいは同一ラック内のシャーシ同士など「小規模な」ラック間接続にはちょうど適切な解と言える。

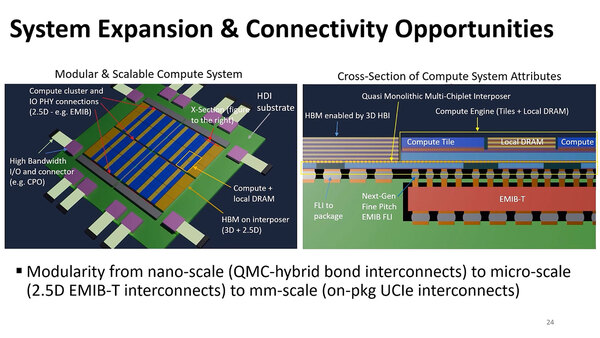

そこで提案としては、微細なところはそれこそ冒頭に説明したHybrid Bonding、大きなダイ同士の接続は引き続きインターポーザーを使った2.5D接続、その外には光インターコネクトという感じで役割分担させるのが現実的と説明する。

OIC/EICはUCIeを使っての接続としている。ちなみにUCIeも2.0で3D接続をサポートしているが、OCI/EICの接続はシリコンインターポーザーないし有機パッケージでの接続を考慮しているようにこの図では見える

さらに将来的には、これをさらにスケールアウト的につなぐとか、Panel Fan Out(現在の300mmウェハーベースではなく、600mm×600mmのパネルベースでパッケージを製造することを前提に、このパネルベースでシステムを構築するという話)などを示した。

今回の話、インテル的にはHybrid Bondingに関してはいろいろ開発が進んでいることもあってか、かなり具体的なリアリティのある話だったのに対し、メモリーやシステムインテグレーションに関してはまだ夢物語に近いレベルの内容も含むものだったのは、まだこのあたりは研究や開発の余地があることの裏返しかと思われる。

とはいえ、チップだけでなくこうしたパッケージ側もなんとかしないと、消費電力や製造コストがとんでもないことになってしまう、という危機感は間違いなく感じられるものだった。

問題は、ではこのメモリーやシステムインテグレーションが現実に提供されたとして、それは記事冒頭で提示した消費電力とメモリー容量の問題解決に十分だろうか? というあたりだろう。残念ながらその解は今回示されなかった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ