現行コンピューターで5年かかる計算を“6万量子ビット”で10時間に短縮

量子コンピューターの早期実用化への道筋を確立、富士通と阪大が新技術発表

2024年08月28日 19時00分更新

大阪大学の量子情報・量子生命研究センターと富士通は、2024年8月28日、量子ゲート式量子コンピューターの早期実用化に向けて共同開発を進める「STARアーキテクチャ」において、「計算規模を拡大する技術(位相回転操作時の位相角の精度向上技術)」、および「量子ビット操作手順を確立する技術」を開発したことを発表した。

この2つの新技術により、現行コンピューターで約5年かかる材料物性計算(ハバードモデル)が、これまでの想定よりも大幅に少ない「6万量子ビット」で、約10時間で実行可能になるという。大阪大学と富士通では「量子コンピュータの早期実用化への道筋を確立した」としている。

量子ゲート式の量子コンピューターは、高い計算能力が期待される一方で、大量の量子ビットを用いなければ計算中にエラーが発生しやすいという課題を持つ。そのため、実用的な計算を現実的な時間内で行うには100万量子ビットが必要になるとされていた。

今回の発表は、そうした計算能力を6万ビットで実現できることを示したもので、量子コンピューターの早期実用化につながる。なお、6万量子ビットは、早ければ2030年頃に実現すると期待されている。

両者が開発を進めるSTARアーキテクチャは、量子計算に欠かせない「位相回転」を効率的に実行することで、より少ない量子ビットでの実用量子計算を可能にする独自アーキテクチャーである。

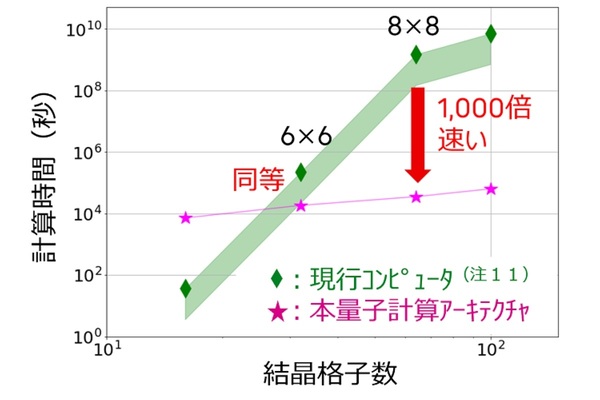

新たに開発した「計算規模を拡大する技術」は、計算規模を決める位相回転操作における位相角の精度を高める技術。精度が落ちないように、位相角の準備方法を再構築した結果、エラーを1000分の1に抑制。これにより、材料物性計算において1000倍の計算規模拡大に成功している。

もうひとつの「量子ビット操作手順を確立する技術」では、量子ビットの操作手順を自動生成する量子回路ジェネレータを構築。これにより、STARアーキテクチャを用いて様々な計算問題を解くための、具体的かつ効率的な方法が得られる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります