磁気ランダムアクセスメモリーMRAMを試作

36.4はMRAMに関する研究である。昨今では先に述べたFeRAMよりもむしろMRAMの方が実現の可能性が高いと見られており、実際第1世代のMRAM(磁界書込式)に続き第2世代のSTT-MRAM(Spin Transfer Torque MRAM:スピン移行トルク式)が主流になり、最近は第3世代としてこのSTT-MRAMを面記憶ではなく垂直記憶として容量密度を上げる方式が研究されている。

その一方でArmとSamsungが共同で、第2世代MRAMに対応したMRAMコンパイラの提供を2018年に始める(要するにSamsung Foundaryを利用する顧客は、自身の製品にMRAMを搭載できる)など、一部実用化も始まっている。

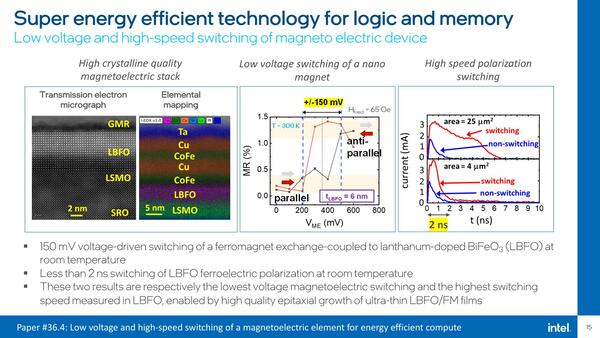

インテルは今回、厚み6nmのランタンを添加したビスマス-鉄系マルチフェロイック薄膜(LBFO)を利用して、アクセス速度2nmのMRAMを試作し、その結果を発表している。

左は薄膜の構成。LBFOの厚みは6nm程度だが、その上下にさまざまな層があるのがわる。中央は電圧とスイッチング確率で、350mV±150mVを掛ければスイッチングできる。右がアクセス時間。Switching(値を変化させる)とNon-Switchingで多少波形は異なるが、面積が小さければ2ns程度でアクセス可能だ

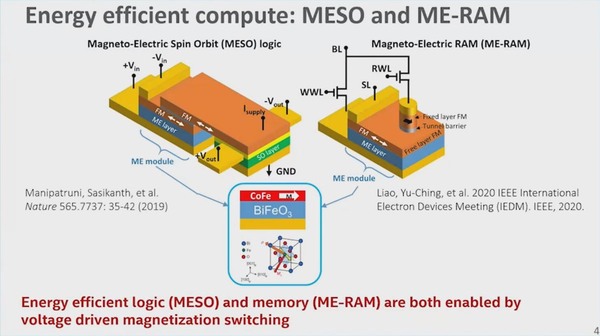

インテルはこのメモリーをME-RAM(MagnetoElectric RAM)としているが、特徴は結構高速なうえに省電力なことであり、単にメモリーだけでなくこれをロジック(MESO:MagnetoElectric Spin-Orbit)デバイスとして使うことも可能であり、非常に省電力なデバイスが構築できる、とする。

ただMESOにしてもME-RAMにしても、CMOSプロセスとの親和性は良い反面、面積効率はCMOSデバイスや前述のFeRAMよりは明らかに悪い。なのでこれは先端プロセッサーというよりもEdge/Endpoint向けという感じで、マイコンなどの構築には良さそうだ。

IFSで将来提供するオプションの1つになるかもしれないという感じではあるが、インテルのプロセッサーにこれが入るという感じにはならなそうである。

発表としてはあと8.4があるが、こちらはQuantum Computing向けの話で、Si/SiGeで構築されるキュービットアレイの欠陥が性能におよぼす影響をどう緩和するか、という話なので説明は割愛する。

以上のようにインテルは、10年先を目指した研究も積極的に行なっている、ということを示した内容であった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ