今回紹介するのはEdgeCortix(エッジコーティックス)という会社だ。2019年に創業という、まだ歴史の浅いAI業界の中でも若い部類に入る。創業者はSakyasingha Dasgupta博士なのだが、実は本社は日本にある。

Dasgupta博士の経歴は少しおもしろく、2015年にドイツのゲッティンゲン大学で物理学の博士号を取った後でなぜか理研に籍を置きながら日本のIBMで研究スタッフとして勤務後に、やはり日本のLeap MindでPrincipal Scientist(主席科学者)のポジションに就いている。

その後、これまた東京のAscent RoboticsでChief Scientific Officer(最高科学責任者)となった後に、なぜかシンガポールのNeuri Pte Ltdという会社のCTO兼CEO代理を務め、2019年7月にEdgeCortixという会社を創業している。

ちなみにEdgeCortixは当初シンガポールと東京の両方に拠点を置いていたようであるが、現在は東京とアメリカ(サンフランシスコ)に拠点を置いている。もっとも同社のウェブサイトを見ると一切日本語がないあたり、本社は東京ではあるものの、あまり日本の会社という感じがしない。

MERAコンパイラとDNAアーキテクチャー

2つのエッジAI推論向けIPを販売

そのEdgeCortixであるが、同社は原則としてチップではなくエッジAI推論向けのプロセッサーIPを販売する会社である。なのでこれを受け取った顧客がASICを作るなりFPGAに入れ込むなりして使う格好になっている。

EdgeCortixが提供するのは、MERA(Multi-module Efficient Reconfigurable Accelerator)コンパイラという、AIのネットワークを同社のハードウェアに落とし込むための専用ソフトウェア、それとDNA(Dynamic Neural Accelerator)アーキテクチャーというハードウェアIPの2つである。

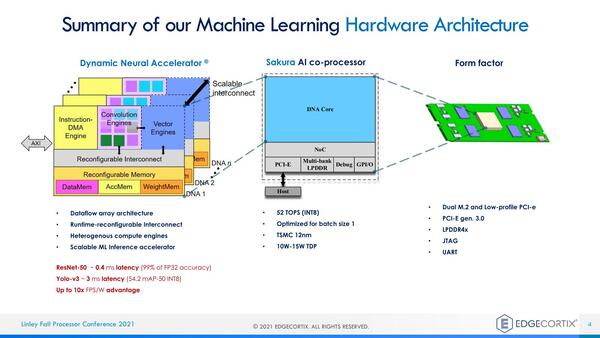

順序は違うが、まずはこのDNA IPについて説明したい。下の画像がその概要である。プロセッサーエレメントの最小単位はそのDNAであり、Convolution EngineとVector Engineの2つの演算要素に対して、これをどう接続するかを動的に変更できるReconfigurable InterconnectとReconfigurable Memory、あとはLocal MemoryとInstruction-DMA Engineが組み合わされたものである。

このDNAのエレメントを集積したのがSakura AI co-processorと呼ばるもので、52TOPSの演算性能を持つ。TSMCの12nmプロセスで10~15WのTDPに収まるそうだ。

そのAI co-processorにLPDDR4メモリーを組み合わせたものがデュアルM.2スロットのPCIeカードとして提供されることになる。もっともこれは評価用ボードという位置づけのようで、製品として提供されるわけではなさそうだ。

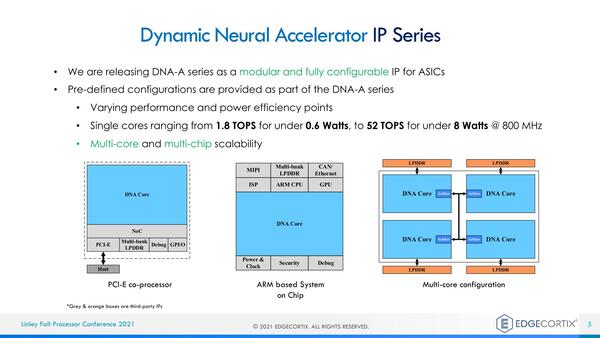

ちなみにこのSakuraにあたるDNAコアは単体で使うこともできるし、PCIe I/Fやメモリーというコントローラーを抜いてSoCのアクセラレーターとして使うこともできる。

また複数のDNAコアをマルチコア構成にしての動作も可能という話であるが、Arm SoCはともかく(*1)、マルチコアの場合にPCIe I/Fはどうなるのか? 単にArbitorだけで協調動作に足りるのか? などいくつか疑問は残る。

(*1) 上の画像を見るとHostとはAXIでの接続になるようだが、SoC側のMemory I/FとAXIだけで帯域が足りるのかどうかはやや疑問ではある。

通常マルチコア構成では、例えばWeightデータの使いまわしなどのためにメモリーをある程度共有したり、データの内容をブロードキャストするといったシステムを組み込むことが多いが、そうしたモノなしにマルチコアで十分スケールする性能が出るのか少し疑問ではある。

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ