チップレットに3D積層を組み合わせた

新しいパッケージX3D

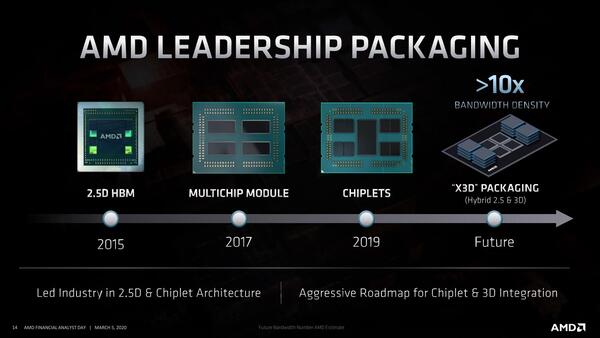

次がパッケージ技術で、今後は現在のチップレットに3D積層を組み合わせたX3Dという新しいパッケージを予定していることを明らかにした。

これは別にCPUに限った話ではない。現在のGPUの場合、連載515回で解説したDeffered Renderingの絡みがあるため、チップレット構成のGPUは作りにくい(*)という欠点があるが、GPGPU的な用途であればこうした使い方はあまり一般的ではないから、実はチップレット式にしやすい。

したがって、RDNAの将来製品は引き続き1ダイの構成が続くだろうが、後述するCDNAの将来製品はこのX3Dを使ったパッケージになっても不思議ではない。

あるいはHPC向けのEPYCなども、ローカルに大量のHBM2を4次キャッシュとして搭載することで、メモリー帯域の不足を補うといった使い方も可能になると思われる。

(*) Deferred Renderingでは、一番最後に各チップレットからフレーム全体への参照が発生する関係で、チップレット間の通信が非常に多くなって、ここがボトルネックになる

CPUとGPUの接続も

インフィニティー・ファブリックで相互接続になる

そのGPUであるが、Radeon Instinct向けのInfinityアーキテクチャーはさらに進化することも紹介された。

第2世代の場合、EPYC 1ソケットあたり4wayなので、2ソケットで8Wayということになる。ただこの場合それぞれの4枚同士はCPUを2つ(と、しかもPCIe Gen4)経由なので、かなり遅くなるのは致し方ない

初代EPYC、つまりNaplesプラットフォームでは4枚のRadeon InstinctをPCIe Gen3で接続する形態だった。

ところが第2世代EPYC、つまりRomeプラットフォームでは、CPUとRadeon Instinctの接続はPCIe Gen4になっただけだが、Radeon Instinct同士はインフィニティー・ファブリックで接続できることは連載485回で紹介した。

これが第3世代EPYCであるMilanプラットフォームでは、CPUとGPUの接続もインフィニティー・ファブリックになることが明らかにされた。

しかもインフィニティー・ファブリック同士が、昔のOpteronのように相互接続可能(これはイメージ図なので、実際はこうはならない可能性もあるが)ということで、大幅に性能が上がることが期待される。

余談だが、このMilanプラットフォームではRadeon InstinctがGPUカードの形をしていないのは、単にスペースが足りないからという可能性もあるが、そもそもインフィニティー・ファブリックを使うならPCIeカードである必要もないわけで、NVIDIAのTesla同様に独自のモジュールでの提供の可能性もありそうに思える。実装面積を抑えるためにも、なにも場所を取って冷却が面倒なPCIeカードを選ぶ必要はないからだ。

ちなみにMilanプラットフォームにおけるインフィニティー・ファブリックの帯域は、現在の2倍になることも明らかにされた。

もう少し先の話をすると、2021年に納入されるスパコンFrontierに加え、2023年にはEl Captainという2 ExaFlopsのマシンをローレンス・リバモア国立研究所に納入することが3月4日に発表された。このEl Captainは次回詳しく解説しよう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ