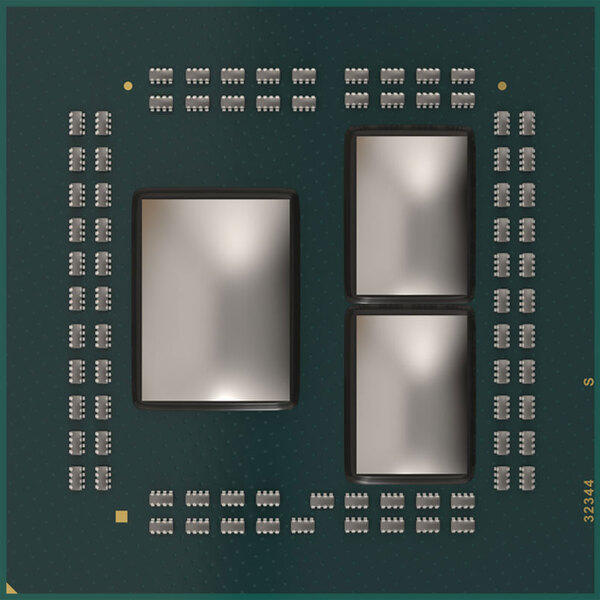

2つのダイを搭載したRyzenは

はたして登場するのか?

連載484回の最後で、I/Oダイは2つのインフィニティ・ファブリックのI/Fを持っており、これを利用して2ダイ構成もあり得ると書いたわけだが、AMD HEROSのCES解説記事の最後で語ったとおり、パッケージに2つ目のダイの配線らしきものが見え隠れしているあたり、この予想が当たってしまったようだ。実際、物理的には現在のパッケージのまま2つのCPUダイを搭載するのは不可能ではない。

このCESの直前に、リークとしてRyzen 9 3800X/3850X、それとRyzen 7 3700/3700Xなるコアが「CESで発表される」というただし書き付きの情報が流れていただが、いくらなんでもこれは無茶である。

というのは、Zen 2コアの前にVega 7nmが製造に入っているわけで、CESのタイミングでRyzenが発表されるのであれば、もうその時点でVega 7nmベース製品が発売されていないとおかしい。

したがって情報の信頼性そのものが果てしなく「?」ではあるのだが、可能性として2ダイ製品がラインナップされることそのものは別に不思議ではない。

ただ筆者からすれば、2ダイ構成の場合は稼働コアを間引き、その分動作周波数を引き上げると思っていた。理由は簡単で、比熱の問題である。

Zenコアに比べてZen 2コアの面積はおおむね1/3程度である。ZenダイとZen 2ダイの組成が大きく変わらないとなると、Zen 2ダイはZenダイに比べて比熱が1/3ほどになる。要するに、同じ消費電力だったら温度上昇の度合いが3倍になるということだ。

ということは、XFR(Extended Frequency Range)などが相対的に効きにくくなる(温度限界にすぐ達してしまう)ことが考えられる。対策としてはもちろん冷却を強化することになるが、比熱を増やすのも一案である。たとえば2ダイながら、どちらのダイも4コアのみ有効とした場合、比熱がZenダイの1/3から2/3に増える計算になる。

おまけに3次キャッシュの容量が2倍になるので、1ダイのCPUに比べて動作周波数の引き上げがはるかに容易になるだろう。オーバークロック用途向けには絶対この構成が適している、というのが筆者の考えである。

このあたりは製品が出てこないとなんとも言えないところではあるが、そう遠くない時期にこのあたりは明らかになると思われる。これは、AMDが言う製品投入時期のMid-2019をどう解釈するか次第であり、第3四半期という話もあるが、もう少し早いと筆者は考えている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ