AMDに対抗して急遽18コア製品まで投入した

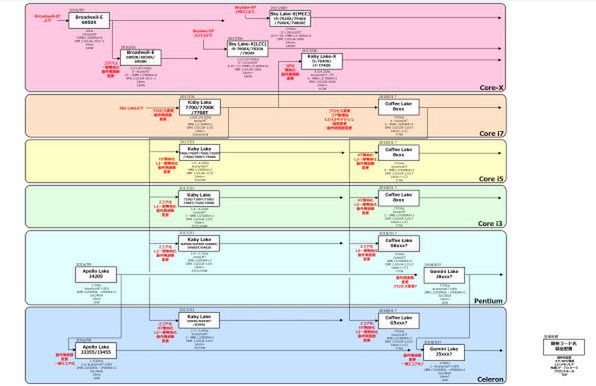

Core-Xファミリー

Xeon Scalableファミリーにからんでくるのが、COMPUTEXで発表されたCore-Xファミリーである。

Core-Xファミリーは、これまでCore i7のExtreme Editionといった扱いになっていたHEDT(High End DeskTop)向け製品を新たに再編したもので、実際ark.intel.comを見ると、これまでExtreme Editionとして扱われてきた製品が全部Core-Xとしてラインナップされ直されている。

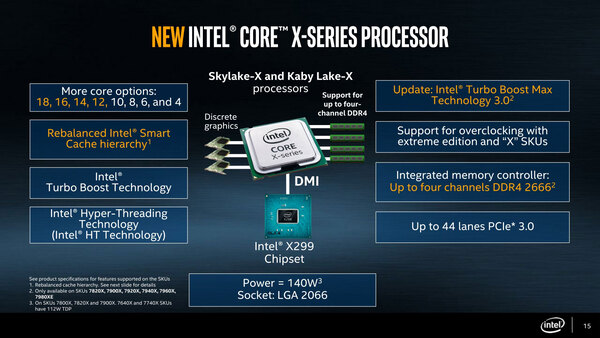

さてそのCore-Xには、Kaby LakeベースのコアとSkylake-SPベースのコアの両方が提供される、という話は連載371回で説明した通り。

予想しなかったのはCore-Xファミリーにi5まで含まれることと、Ryzen Threadripper対抗で急遽18コアの製品まで投入することを決めたことだ。

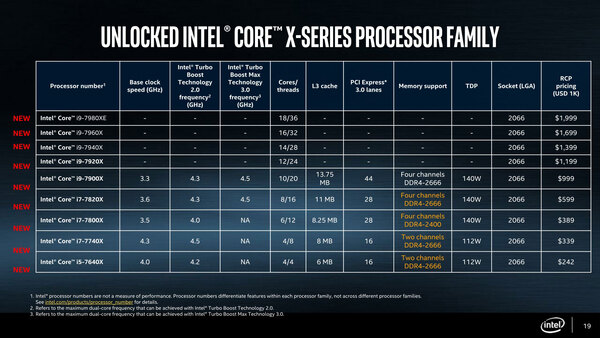

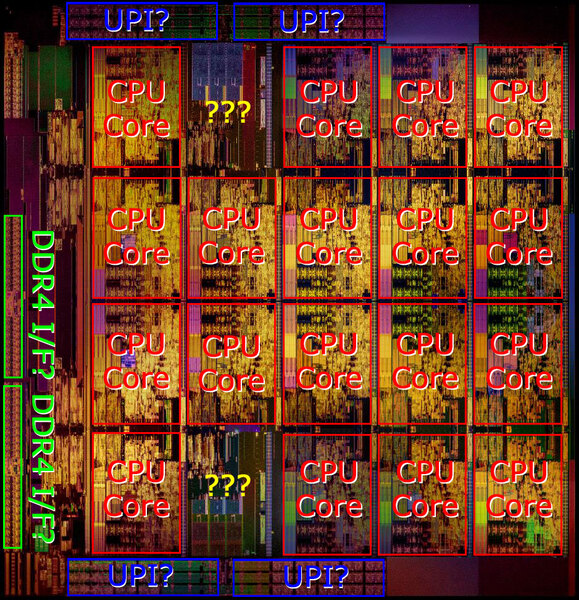

当初はCore i9-7920X相当の製品がハイエンドだったらしい。ここまでだとLCC(Low Core Count:最大12コア)のダイでカバーできる。ところがRyzen Threadripperが16コア/32スレッドというお化けスペックを実現したため、急遽MCC(Middle Core Count:最大18コア)の製品を追加することになった。Corei i9-7940X~7980XEのスペックが全部空白になっているあたりがこれを物語っている。

またCore i9-7920Xについては、急遽ハイエンドからミドルレンジに製品ポジションが変わってしまった関係で、スペックが一旦白紙に戻った模様だ。

Core-Xファミリーと組み合わされるチップセットがX299である。資料を見るとDDR4が4ch、PCI Expressが最大44レーンとあるが、これはCore i7-7900X以上の場合にのみフルサポートで、特にKaby Lakeコアを利用した場合はDDR4は2ch、PCI Expressは16レーンに限られることになる。

ところで、ここで再びXeon Scaalableファミリーの話に戻るのだが、今回ハイエンドにあたる18コア製品のダイ写真が公開された。

このダイのレイアウトを抜き出して分析してみたのが下の画像である。そもそもコアのサイズ(縦横比)が従来と異なっているのがわかると思う。

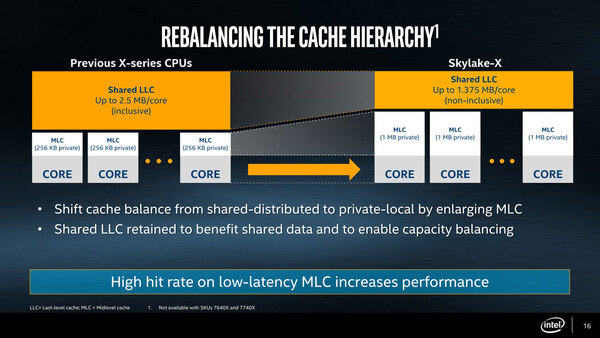

実はCore-X(=Xeon Scalable)では、2次キャッシュ(インテル用語ではMLC:Middle Level Cache)と3次キャッシュ(同LLC:Last Level Cache)の構成が大きく変更になった。

- 2次キャッシュは、これまでのコアあたり256KBからコアあたり1MBに増量

- 3次キャッシュは、これまでのコアあたり2.5MBから、コアあたり1.375MBに減量

- 3次キャッシュがNon-Inclusive(事実上のExclusive)構成になった

コアあたりで言うと、これまで2.75MBのキャッシュが利用可能(ただしInclusiveなので実質2MB)だったのが、今度からコアあたり2.375MBということになり、若干利用できるキャッシュ量が増えている。

またレイテンシーの少ない2次キャッシュが4倍に増量されたことで、大量データを扱うようなケースを除くとおそらく性能の改善につながる。

問題はXeon Scalableがまさしく大量のデータを扱うようなワークロードに向けた製品なことで、これは理屈に合わない。このあたりはまだ筆者も完全に理解しきれていないので、今後もう少しインテルから資料が出てきたら、改めて解説することにしたい。

話を戻すと、Core-X向けのSkylake-SPコアは、14nm+を利用し、しかも2次/3次キャッシュの構成変更で若干の性能上乗せが期待できる。

Ryzen Threadripper向けに「できることは全部やりました」という感じで、Athlon 64の発表に向けてPentium 4でハイパースレッディングを有効にしたり、DDR-400をサポートしたりした故事を思い出す。

ちなみにそのCore-Xの製品投入時期であるが、Kaby Lake-Xベースのものはわりとすぐ、Skylake-SPのLCCのものもやはり比較的早期に投入されるだろう。ただ本命のSkylake-SP(MCC)のものはやや遅れるようで、ヘタをすると8月くらいになりそうだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 - この連載の一覧へ