前回に引き続き、今回もRyzenの話だ。今回は、2017年2月5日~9日にかけてサンフランシスコで開催されたISSCC 2017におけるAMDの発表資料を元に、Ryzenの内部構造、主に回路的な工夫について解説しよう。

このうちいくつかの項目については、連載372回で説明したHotChipの内容とやや被ることをあらかじめお断りしておく。

FPUの改良で消費電力を15%改善

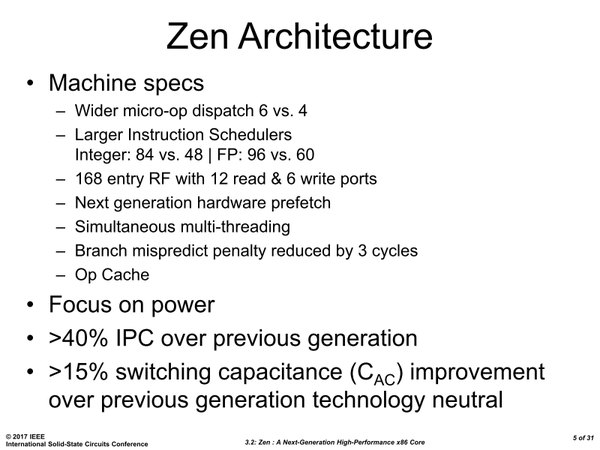

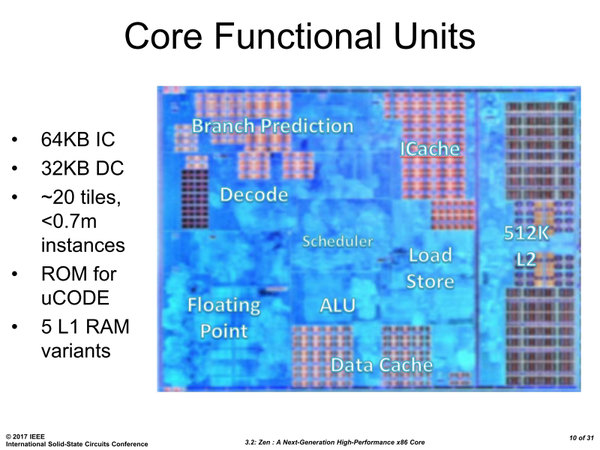

まず下の画像が基本的な要件である。x86命令レベルでは1サイクルあたり4命令のデコード構造だが、内部のmicro-opレベルでは1サイクルあたり6命令の処理が可能とされる。

これにあわせて、Register File(演算の際に利用するレジスタの物理的な格納場所)の数もExcavator比で大幅に増やされている。またキャッシュ/メモリーに対するロード/ストアーのバッファも合計168エントリー装備され、リード 12/ライト 6の処理ポートが搭載されるという重厚な構成である。

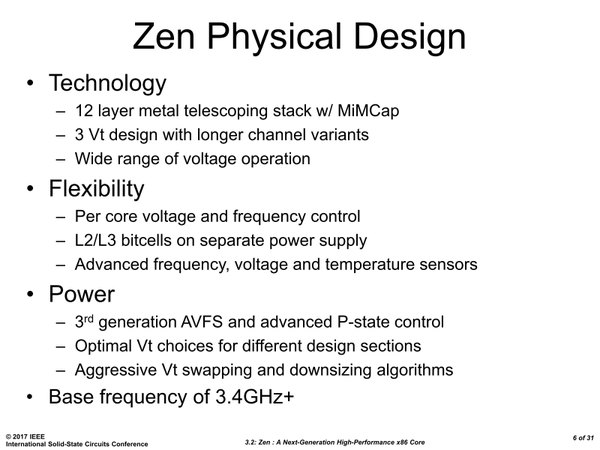

このあたりまではHotChipsの説明とそう変わらないのだが、追加されたのは消費電力に関わる部分だ。IPCを40%以上改善するとともに、スイッチングの容量(≒スイッチングに要する電力)を15%以上改善する、としている。これを実現するための特徴として、以下の特徴が示されている。

- MiMCapを採用(これは後述)

- 内部は3種類の電圧供給とする

- コア毎と2次/3次ャッシュは電圧プレーンを分離する(つまりコアとあわせると1つのCore Complexに5種類の電源プレーンが存在する)

- 第3世代のAVFS(Adaptive Voltage Frequency Scaling)を採用する

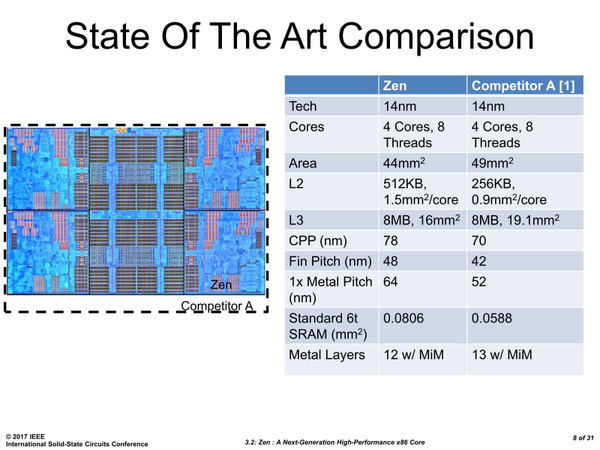

まず、コア(4コア+8MB 3次キャッシュ)の構成を、インテルのおそらくはSkylake世代と比較したと思われる数字がこちら。

同じ4コア/8スレッドであるが、2次キャッシュはSkylake比で倍の容量なのに、全体としてはRyzenの方がエリアサイズが小さく収まっている。

実際に比較すると、Fin Pitch(FinFETのFinの間隔)は48nm vs 42nm、CPP(Contacted Poly Pitch)は78nm vs 70nmということで、トランジスタの最小サイズはZenの方が27%ほど大きくなる。

そもそも昨今では、14nmプロセスと言いつつも、実際には14nmの寸法になっている部分は1つもない。その代わりにFin Pitch(プレナー型トランジスタの場合はTransistor Pitchなどとも呼ぶ)とCPPを使ってプロセスの大きさを判断することが普通だ。

これに関しては以下の経験則(ASML Formula:ASMLの法則)がある。

ノードサイズ=0.14×(CPHP×MMHP)^0.67

CPHPはCPPの半分、MMHPはFinPitchの半分をそれぞれ示す値で、上の数字を使うとRyzen(GlobalFoundriesの14LPP)は13.70nm、Skylake(インテルの14nm)は11.66nm相当になる。

要するにインテルの方が攻めたプロセスを利用しているわけで、同じ回路サイズならばRyzenの方がエリアサイズが大きくなるはずであるが、これを小さくまとめることができた、というのがRyzenの特徴である。

理由の一端は、FPU回りにある。Ryzenでは512bit幅のAVX-512をサポートしない。

正確に言えばこれが実装されているのはXeon PhiとSkylake-EP/EXというXeon向けのコアのみで、デスクトップ向けのSkylakeやKabylakeでは無効化されているが、無効化されているだけで回路としては存在する。

結果、例えばAVXレジスタの量は4倍に増えている。初代のAVXレジスタは、SSE用のXMM0~XMM15という16個のレジスタ(128bit幅)を256bit幅に拡張したYMM0~YMM15が用意されるが、AVX512用にはこれをさらに512bit幅にするとともに、数を倍にしたZMM0~ZMM31が用意される。このスペースは馬鹿にならない。

当然FPUも倍の数が必要になるし、512bit幅のデータのロード/セーブを行なうために、ロード/ストアーユニットはRyzenの2倍にあたる4基が搭載される。当然データバスの幅もそれだけ確保しなければならない。

こうして考えていくと、AVX512を搭載するためのコストはけっこう高いものになる。実際AMD CTOのMark Papermaster氏が、質疑応答の中で明確に答えてくれた。

「AVX512の搭載は当初から考えていなかった。理由は2つある。1つはコストが高くつくことだ。もう1つは、もしそこまで浮動小数点演算性能が必要なら、我々は良いGPUを持っているから、こちらを使えば済む」

このあたりの割り切りも、小さなダイエリアの実現に貢献していると思われる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ