Zenの内部構造を予想

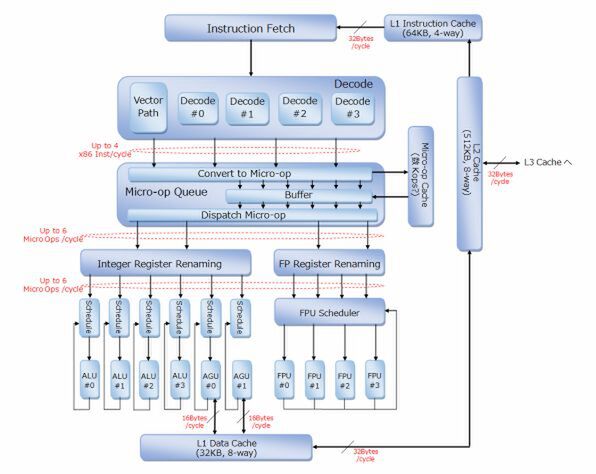

下図は、連載332回で紹介した内部構造図のアップデートである。

デコード段のFast PathとVector Pathは、図が複雑になるだけなのでまとめてしまった。またRegister Fileは省略している。

現段階で不明なのは、Micro-op Queueの実態である。上では「要するにDispatch Unit」であると書いたが、そして実際ディスパッチの機能は持っているが、それ以外にデコードされたx86命令をMicro-opに変換するのもこのステージである。

ここではMicro-op Queueと1つのブロックにからめたが、内部的には連載332回で示したように2段階になっており、最初のステージではx86からデコードされた中間命令をμOpに変換する作業、2つ目のステージが変換されたμOpをディスパッチする処理で、この2つのステージの間にバッファが入る、という構造ではないかと思う。

そしてMicro-opキャッシュはコンバート後のMicroOpを、おそらく数KOps保持する構造と思われる。構造的にMicro-opキャッシュが効果を上げるのは、プログラムのループ構造を丸ごと保持するようなケースである。

数百Opsでは、やや複雑なループであふれてしまうし、数十KOpsでは1次キャッシュより大きくなってしまいかねないため、根拠のない直感で言えば2~4KOpsあたりではないかと予想する。

不明なのは他にもあって、Summit Ridgeは8コア構成だが、このコア同士がどう接続されるかが現時点でははっきりしない。Bulldozer世代では4モジュール/8コアをファブリックで接続し、このファブリックに3次キャッシュも接続されるという構成だったが、この方式を踏襲するかどうかは不明である。

ただ、こうした事柄はまもなく開催されるHotChipsでもう少し詳細が明らかにされることを期待したいところだ。

Socket AM4用のチップセット開発が難航?

以上が公式に発表された情報を基にした話であるが、以下では非公式情報を若干お届けしよう。まずは動作周波数であるが、今回のデモで3GHz駆動は問題なくできることが示されている。実際の動作周波数はBase 2.8GHz/Turbo Core動作時3.2GHzといったスペックになりそうである。

そしてその際のTDPは、4コア/8スレッド品が65W、8コア/16スレッド品が95Wという数字はほぼ確定のようだ。連載333回で、3GHz程度の動作周波数でTDPが60W程度と推定したが、おおむね合致したようでほっとしている。

Summit Ridgeそのものは順調に推移しているようだが、これをサポートするはずのSocket AM4プラットフォームがさっぱり出てこないのが現時点での問題である。

実際Socket AM4を普及させるための露払いの役目をBristol Ridgeが担うことになっていたはずなのだが、これが出ないのはBristol Ridgeの問題ではなく、Socket AM4用のチップセットに問題がある、という話が出ている。

詳細は明らかでないが、USB向けにReTimerチップが必要なんて話があるあたり、「またか」という気になる(連載203回参照)。

ReTimer、という用語はPCI Expressのものであるが、単純に言えば信号のリピーターである。USBは3.0以降でPCI Expressの規格を利用している(3.1では物理層は独自になったが、その上は引き続きPCI Expressをベースにしている)のだが、PCI Expressでは特に信号速度が上がった場合には通信できる距離が限られる。

これは伝達時間の問題ではなく、距離が伸びると信号が急速に劣化してまともに通信できなくなるという話である。

ただ通信できる/できないを判断するのは、最終的に「所定の時間内に定められた信号が来るかどうか」で判断するわけで、そのためにPCI Expressデバイスは内部に一種のタイマーを持っており、ここでタイムアウトが発生すると通信失敗と判断するわけだ。

そこである程度の距離を伸ばす場合、間にリピーターを挟んで信号品質を改善するわけだが、この際にリピーターを挟むタイミングでタイマーを一度0クリアして時間を数え直すことになる。この「タイマーをクリアして数え直し」という動作からReTimerという呼び方がなされている。

話を戻すと、Socket AM4では基本的にUSB 3.1のコントローラー(xHCI)そのものはCPU側に入っており、ここから信号をチップセット側に引っ張り出してマザーボード上のコネクターにつなぐ、という形での実装を考えていたらしい。

しかし、この方式では配線長が限界を超えてしまうのか、他になにか信号が劣化する要因があったか判断できないが、とにかくReTimerを挟まないと通信できないという問題が出ており、この対処に手間取っているという話であった。

このあたりをどう解決されるのかはまだはっきりしないが、これが理由でSocket AM4自身が出てくるのはほとんどZenと同じタイミングという可能性も出てきたのは、デスクトップ向けのBristol Ridgeがスキップされるという意味でもあって残念である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ