速度を大幅に高速化し、

メモリーもDDRからDDR2に変更

BlueGene/Pは、PowerPC 450コア(+FPU)を4組組み合わせたマルチプロセッサー構成である。その概略が下の画像で、各々のコアには2次キャッシュが搭載されている。

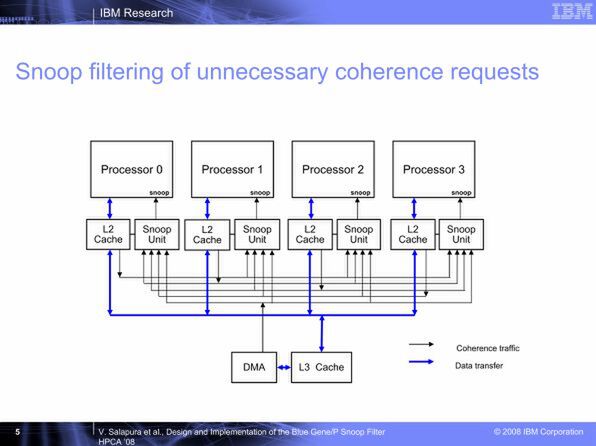

ちなみに、いくら探してもこの2次キャッシュの容量が記載されていないのだが、後述のダイ写真から推定すると16KB程度だろう。そのダイ写真を見ると2次キャシュが共有のように見えるが、実際にはコア毎に個別になっており、かつそれぞれスヌープユニットが付きキャッシュのスヌーピングを処理しているようだ。

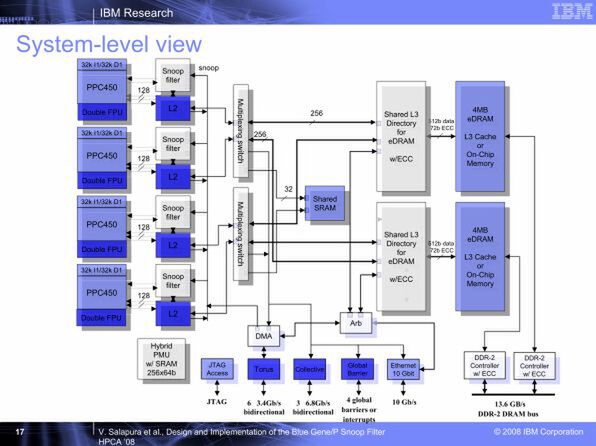

2次キャッシュを含めたチップ全体の構造が下の画像で、2コアづつまとめてMultiplexing Switchを通して、共有SRAMや4MB×2の3次eDRAMに接続されるといった構造は、多分にBlueGene/Lのチップの構造を部分的に継承しているためだろう。

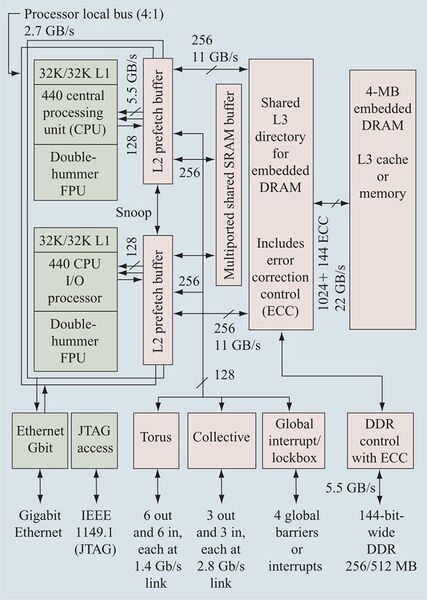

ただ、下にあるBlue Gene/Lのチップ構造と比較するとわかるが、外部とのリンクに関しては数そのものは同じだが、速度は大幅に高速化されており、メモリーもDDRからDDR2に変更されるなど性能の底上げに貢献している。

もっとも1つのチップあたりのコア数は倍増しているので、このくらい性能を上げないと辻褄が合わないということかもしれない。

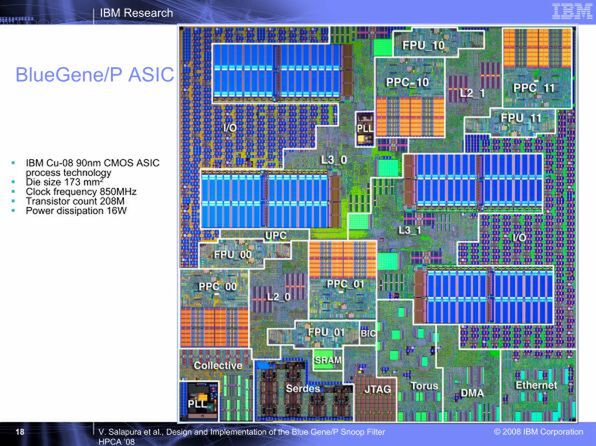

さてそのダイが下の画像である。全体としてはかなりよく頑張ったというか、苦労して収めた感じがよくわかる。

先の2次キャッシュがコアあたり16KBというのは、この写真における2次キャッシュ領域のSRAMアレイの面積を、PowerPCコアの1次キャッシュと思しきSRAMアレイと比較しての考察である

プロセスは90nm銅配線のCu-08を利用し、850MHz動作で16Wとなっている。ダイサイズ173mm2、トランジスタ数2億800万というのは、同じ90nmプロセスを使ったインテルのPentium 4が112mm2でトランジスタ数1億2500万個と比較すると、トランジスタ密度は同程度である。

ただしPentium 4が3.4GHzまで動作周波数が上がる代わりにTDPは89W、他方BlueGene/Pは850MHzに抑えてTDPは16Wである。SIMD演算を除外して純粋にFPUの性能を比較すると、倍精度演算の場合Pentium4は3.4GFLOPS、一方BlueGene/Pは13.6GFLOPSということで、ダイサイズこそやや大きめながらBlueGene/Pの性能の高さや性能/消費電力比の良さがわかる。

→次のページヘ続く (ほぼ2倍のプロセッサー密度を実現)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ