東芝は6月10日、新方式磁性体メモリを使うことでプロセッサの消費電力を60%低減できるキャッシュメモリ回路を開発したと発表した。

新方式メモリはSTT-MRAMと呼ばれ、同社が研究開発を続けてきたもの。電流を流すと素子の磁気スピンとして記憶されるスピンエレクトロニクスデバイスの一種で、原理的には電源を切っても内容が失われない不揮発メモリ。

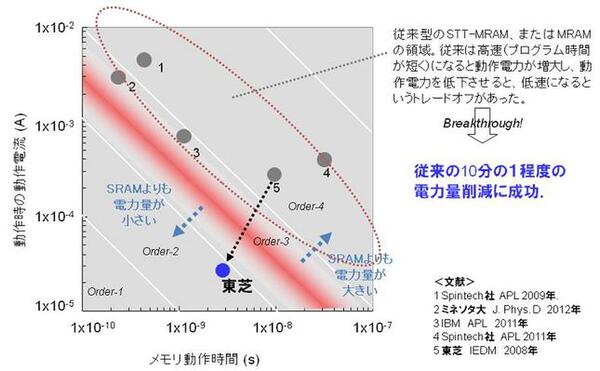

STT-MRAMをキャッシュメモリとして利用するには高速性能と低消費電力を両立させるのは困難だったが、新たに2つ素子を用いた回路設計を行った。シミュレーションによると、この回路を用いた高容量キャッシュメモリはプロセッサの速度を落とすことなく消費電力を60%減らすことができるという。

この技術開発は、NEDO(新エネルギー・産業技術総合開発機構)のプロジェクト「ノーマリオフコンピューティング(必要な部分以外には電流を供給しなくても全体的には問題なく動作する低消費コンピュータ技術)基盤技術」として進められており、2015年までには消費電力を10分の1に抑えることができる不揮発キャッシュメモリの開発を目指す。

■Amazon.co.jpで購入