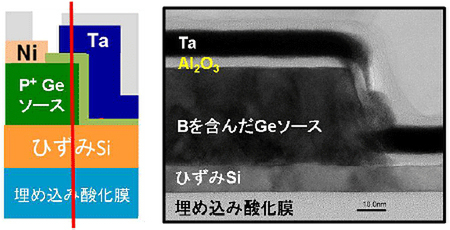

GeソースとひずみSiチャネルの近傍の素子構造(左)と試作された素子の断面透過電子顕微鏡写真の拡大図(右)

東京大学と科学技術振興機構は12月15日、極めて低い電流でも動作するトンネル電界効果トランジスターを開発したと発表した。

科学技術振興機構のJST戦略的創造研究推進事業の一貫として研究が進められているもので、半導体中のエネルギー障壁を越えて電流が流れる量子力学的トンネル電界効果を利用する素子。従来のMOS型のFET(電界効果トランジスター)に比べて飛躍的な効率化が期待されているが、ON電流とOFF電流の差を大きく取れないといった問題があった。

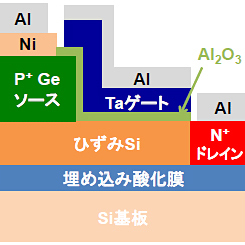

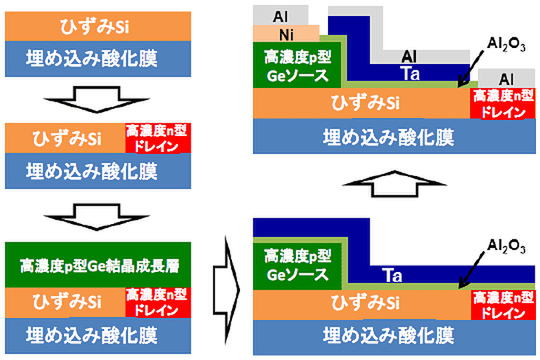

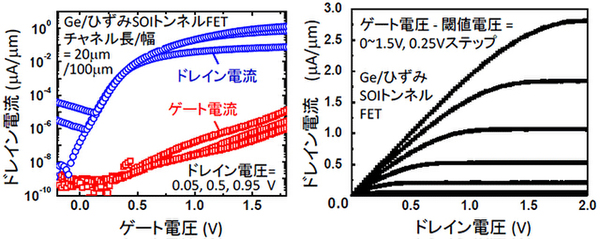

東京大学大学院工学系研究科の研究グループは、シリコンに応力を加えることでバンドギャップや移動度などの物理的な特性を変化させた「ひずみSi」を用い、従来からの集積回路と同様な半導体材料の組み合わせ・製造方法ながらも極めて薄いエネルギー障壁幅を形成した。試作したトンネルFETは、ON電流とOFF電流の比が107というこれまでのトンネルFETで最も大きい値を実現となった。この素子を用いることで、0.9~0.3V以下にまで電源電圧を低下しても動作する集積回路の可能性があるという。

現在のシリコントランジスターの製造工程と整合性の高い方式によってトンネルFETが制作できることがわかり、現在の集積回路に組み込むことで消費電力の低減、素子微細化の限界を超える回路の実現、無給電で長期間動作する素子など、さまざまな可能性を持つとしている。

■Amazon.co.jpで購入