キャッシュの仕組み解説編最後のテーマは、「コヒーレンシ」(Coherency)である。あまり耳にしない単語だが、直訳すると「首尾一貫性」といったところか。キャッシュの場合、この単語は「データの一貫性」「データの整合性」といった意味合いで利用される。これは、前回触れた複数レベルのキャッシュで問題となる場合もあるが、一番大きな問題が起きるのは、マルチプロセッサー/マルチコアCPUの環境である。

マルチプロセッサー環境でキャッシュの整合性を保つ

スヌーピングとその方式

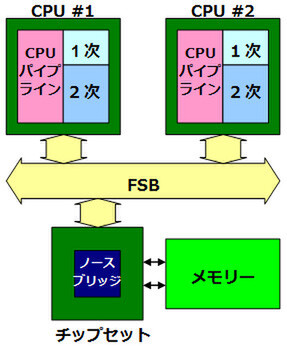

例えば図1のような、懐かしいデュアルCPU構造を例にとって見る。ここで「CPU #1」があるデータを書き換えたとする。

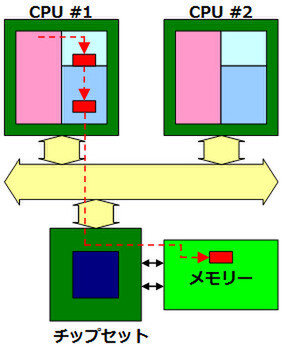

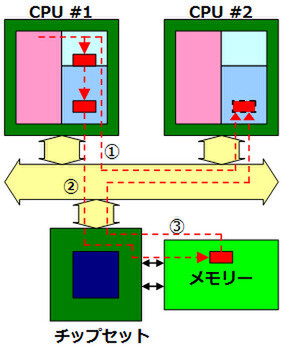

すると、図2のように1次/2次キャッシュの更新を経て、最終的にメモリーにそれを反映して終わる。ここまではいい。問題は「CPU #2」である。もしCPU #2が同じアドレスのデータをすでにキャッシュしていたとすると、CPU #1がデータを書きこんだことで、CPU #2のキャッシュとデータが一致しなくなる。これを避けるために、実際は以下の手順をとる(図3)。

- ①CPU #1はキャッシュに書き込むとともに、CPU #2側に書き込んだメモリーアドレスを通知する。

- ②通知を受け取ったCPU #2が、当該アドレスをキャッシュしている場合、これを無効化する。同時にCPU #1は書き換えた内容をメモリーに反映する。

- ③もしCPU #2がそのデータを必要とする場合、もう一度メモリーからフェッチする。

この一連の操作は「スヌーピング」(Snooping)と呼ばれており、FSBのバスプロトコルの中には、このスヌーピングに必要なキャッシュ制御機能が含まれている。このバスプロトコルにはさまざまなものがあるが、x86系で広く使われているのが「MESI」プロトコルである。これはキャッシュの状態を以下の4種類で管理すると言う方法だ。

| M | E | S | I |

|---|---|---|---|

| Modified | Exclusive | Shared | Invalid |

| 変更あり | 変更なし/他CPUになし | 変更なし | 無効 |

各々の状態の頭文字をとって「MESI」となるわけだが、ほかにも以下のようなキャッシュ管理プロトコルが考案されており、実際にこれらを実装したCPUが存在する。

| MSI | Exclusiveがない |

|---|---|

| MOSI | Exclusiveの代わりに「Owned」という状態が入る |

| MOESI | MESIにOwnedを追加 |

| MERSI | MESIに「Read only or Resent」が追加 |

| MESIF | MESIに「Forward」が追加 |

一般論として、簡単なプロトコルにすればスヌープ自身のオーバーヘッドは減るが、その分制約が生じる。例えば、MSIプロトコルはExclusiveを持たないため、「あるメモリーのコピーは、特定のCPUのキャッシュだけにある」=「そこを書き換えてもスヌープの必要はない」状態であっても、これを示す方法がない。

そのためCPUからは、「すべてのCPUのキャッシュに、そのメモリーのコピーがある」のように見えるので、そのデータを書き換えると、必ず全CPUに対してスヌープが発生する。しかし、むやみやたらとキャッシュの状態(ステート)を増やすと、今度は状態の管理によるオーバーヘッドが問題になる。そのためMESIプロトコルは、比較的バランスが取れたものとして広く利用されている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ