トランジスターを増やさずに実装できるSMT

話を戻すと、こうしたスレッドはしばしば、同一のプロセスに属している。これを前ページ図1のようなデュアルコア構成でロードする場合、結果的に両方の1次キャッシュに同じプログラム/データがロードされかねず、無駄が多い。であれば、「同時に複数のスレッドを実行できるようにすれば、キャッシュの効率も上がるし、実行ユニットの効率も上がるのでは?」というアイディアが出てきた。これがSMTである。

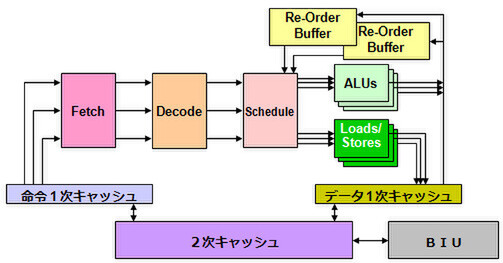

具体的にはどんな形になるのか?というのが図2である。一見Re-Order Bufferが増えているだけであるが、これは実のところあまり正確ではない。

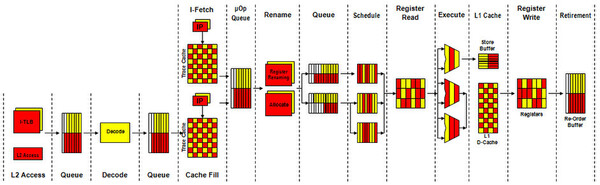

図3は、インテルが「Pentium 4」で実装したHyper-Threadingでの、内部構造をまとめたものである。Cache Fillに到るまでが2段に分かれているのは、上段がTrace Cacheにヒットした場合で、下段がキャッシュミスで2次キャッシュから命令を取り込んだ場合である。赤と黄色は、それぞれの別のスレッドの命令/データであることを示している。

図3にあるように、基本的にはパイプライン構造はまったく同じであるが、以下のユニットはそれぞれのスレッドにあわせて、二重化されている。

- IP(命令ポインタ)を含む汎用レジスター

- TLB(Translation Look-aside Buffer)

- Register Renaming/Allocate

また、各種キュー(Queue)やμOpキュー、Re-Order Bufferなどは、内部を2分割してそれぞれのスレッド別に管理できるようになっている(キュー/バッファーのサイズは一緒)。その一方で、1次キャッシュ(Pentium 4の場合はTrace Cache)やスケジューラー、実行ユニットなどに関しては、2つのスレッドで混在して処理されるようになっている。

見かけよりはいろいろ細工が多いSMTであるが、見ておわかりのとおり、バッファーそのものが増えている部分はごくわずかだ。大半はスレッド判別用にバッファーの各エントリーを1bit増やしたとか、その1bitでどちらのスレッドを処理しているかを判断するロジックを増やしたといった、細かな作業に費やされている。

結果として、例えばPentium 4の「Willamette」コア(と恐らくNorthwoodコア)では、「Hyper-Threadingを搭載することでダイサイズが5%増えた」と報告されている。現行の「Nehalem」コアの場合、正確な数字こそ発表されていないが、IDF Fall 2007でパット・ゲルシンガー氏(当時のインテル上級副社長)が、「そもそもSMTはエレガントな設計。リソース・リユースの観点から見ると、4~5%のダイ面積増加で、最高だと30~40%の性能向上がある」と語っており、やはり同程度のダイサイズ増加で実現できるものと見られる。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ