最初から倍精度対応を見据えたSSEの実装と

トランジスター数による限界

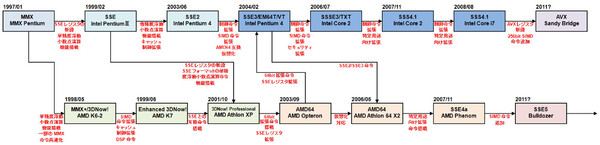

拡張命令から見るx86 CPUの第2回を始めよう。まずインテルは、1999年2月にリリースした「Pentium III」で、「KNI」(Katmai New Instruction)こと「SSE」(Streaming SIMD Extension)を導入した。名称冒頭の「Streaming」は単なるマーケティング的な用語であり、少なくともこの時点でのSSEには、ストリーミング的なデータを扱う機能は一切なかった。

それはともかく、このSSEはインテルのある種明確な意思を感じる。それは「SSEはMMXを置き換えるもの」という事だ。これはAMDの「3DNow!」と比較すると明確である。3DNow!とは、MMXに浮動小数点演算機能を付加するための、いわばMMXの拡張という扱いだ。整数演算はMMX任せということで一切サポートしておらず、またレジスターもMMX同様に、浮動小数点演算(FP)レジスターの64bit分をマッピングしたMM0~MM7のレジスターを使って演算する(FPレジスターそのものは、IEEE854の拡張精度をサポートするため80bit分ある)。

これに対してSSEでは、新たに128bit幅のXMM0~XMM7のレジスターを定義し、このレジスターに対する単精度浮動小数点演算命令を新規に用意している。整数演算はSSEには含まれないので(後述)、その点ではSSEと3DNow!はどちらも「MMXに浮動小数点演算能力を追加」と言えなくもないのだが、レジスター互換性をあっさりと放棄した事は大きい。実際、これに続くSSE2では整数演算も追加され、結果としてMMXのニーズはほとんどなくなっている。

これは命令セットからもあきらかだ。基本的には、MMXもSSEもレジスター間演算なので、対象となるレジスターを新たに追加したら、命令の互換性が失われるのは当然とも言える。ではなぜSSEに128bit長のレジスターを追加したかと言えば、恐らくはSSE2の世代で、倍精度浮動小数点演算に対応することを当初から予定していたためだろう。倍精度浮動小数点の格納には64bitが必要になるから、MMXレジスターをそのまま流用すると、値がひとつしか格納できず、これではSIMDの意味がないからだ。

もっとも、XMMレジスターの実装に大量のトランジスタを割いたこともあり、それほど大規模な演算ユニットを実装することはできなかった。128bit長のレジスターが8個というのは、通常の32bitレジスターを32個追加することに相当する。昨今の製造プロセスを使うのであればたいした分量ではないのだが、1999年当時のプロセスでは、この実装は容易ではなかった。

当初登場したPentium IIIは、0.25μmプロセスを使うKatmaiコアだったが、同じ0.25μmプロセスを使ったDeschutesコアのPentium IIと比較すると、トランジスター数とダイサイズはこうなる。

| CPUコア | トランジスター数 | ダイサイズ |

|---|---|---|

| Katmai | 950万個 | 128mm2 |

| Deschutes | 750万個 | 118mm2 |

つまり、これ以上機能を詰め込むのは無理だった。なにせ当時は2次キャッシュをオンダイ(CPUと同じダイ)にするのも難しく、Pentium IIや(Katmaiベースの)Pentium IIIは、2次キャッシュ用のSRAMを別チップで搭載していたほどだった。性能面での寄与や低コスト化を考えると、2次キャッシュをオンダイにするほうが先であり、SSE用に大規模な演算回路を突っ込む余地はほとんど無かった。

その結果、Pentium IIIのSSEの処理性能は、3DNow!を備えたAMDのK6-2などとたいした差がなかった。Pentium IIIの場合、1個のXMMレジスターに4つの単精度浮動小数点の値を格納してSIMD演算ができるが、演算のスループットは2サイクルだった。対するK6-2は、MMXレジスターに2つの単精度浮動小数点の値を格納して演算するが、演算のスループットは1サイクルである。つまり、十分に最適化できれば同一周波数のPentium IIIとK6-2は同じ演算性能となるわけで、この時点での性能差はない状況だった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ