|

|---|

| AMDのテクノロジー戦略について語った米AMD CTOのフィル・ヘスター氏 |

日本エイ・エム・ディ(株)(以下AMD)は8日、東京都内のホテルにて報道関係者を対象としたテクノロジー戦略説明会を開催し、2006年以降のサーバーからモバイル分野に及ぶ同社の技術開発の戦略について説明した。クアッドコアCPUやCPUのモジュラーデザイン、CPUコア以外に特定用途の高速化に特化したアクセラレーションプロセッサーを使う新技術“Torrenza(トレンザ)”など、同社が研究・開発中のさまざまな技術について紹介された。

この説明会は米AMD社が1日(現地時間)に開催したアナリスト向けミーティングで披露された話題を、抜粋して日本の報道関係者向けに紹介したもの。説明は米AMD CTO(最高技術責任者)のフィル・ヘスター(Phil Hester)氏が担当した。米国では複数の同社幹部が4時間かけて行なったものを、1時間に圧縮して行なう駆け足の説明会だったが、説明された技術には今後のサーバーやデスクトップパソコンに関わる興味深いものが多数見受けられた。

CPUのモジュラーデザインとクアッドコアCPU

|

|---|

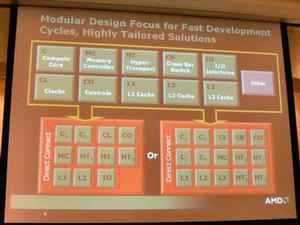

| CPUに搭載する機能別にモジュラー化し、用途に応じて必要なモジュラーを組み合わせてCPUを作る“モジュラーデザイン”の概念図 |

顧客によってCPUに対するニーズも異なり、多様な製品が求められる現状に対応し、効率よくCPU開発を行なう手法として取り上げられたのが、CPUの各機能ブロックをモジュラー化し、必要なモジュールを組み合わせてひとつのCPUを構成する“モジュラーデザイン”である。Athlon 64などの場合、CPU上にはCPUコア、キャッシュメモリー、メモリーコントローラー、HyperTransportリンク(HT)などの機能が搭載されている。これらをそれぞれモジュラー化して、たとえばコンシューマー向けデスクトップ用CPUならば、「コアを2つ、適当な量の1次/2次キャッシュメモリー、HTを1つ」といった構成に、マルチプロセッサーサーバー向けCPUならば、「CPUコア4つ、HTを3~4つ、キャッシュメモリーは大容量の3次キャッシュも搭載」といった構成でCPUを設計する。モジュールを組み合わせて市場セグメントに合わせたCPUを構成できるようにすることで、開発にかかるコストを低減できるというわけだ。同様のコンセプトは米インテル社も提唱している。

|

|---|

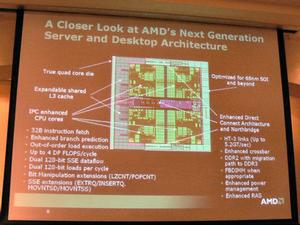

| AMDの次世代クアッドコアCPUアーキテクチャーのダイ写真。モジュラー構造を強調するために色分けされているが、きれいに分割されている |

AMDは2007年にクアッドコアのCPUをサーバー向けとデスクトップ向けに提供する予定である。写真で公開された次世代のサーバー&デスクトップパソコン向けCPUアーキテクチャーのダイ写真では、4つのCPUコアや共有化された3次キャッシュメモリー、I/Oインターフェース部分がきれいに色分けされたブロックで構成されていた。

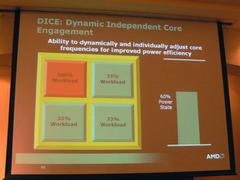

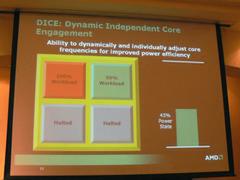

またヘスター氏は「顧客が重要視するのは電力である」と述べ、消費電力低減技術として“DICE(Dynamic Independent Core Engagement)”を紹介した。これはCPU内のコアごとに異なるクロック周波数を供給する技術で、各コアの負荷に応じて動的に周波数を変更することで、CPU全体の消費電力を下げる。これによりデスクトップパソコンからデータセンターまで、効率よい電力消費を実現できるという。ヘスター氏は2006年のCPUと比較して、2007年のCPUでは消費電力あたりのパフォーマンスが60%向上し、2008年のCPUでは150%もの向上を実現するだろうとの見方を示した。

|

| |

|---|---|---|

| 4基のCPUコアのうち、1つだけが100%負荷で、他は33%程度の場合、コアに供給するクロックを下げて全体の消費電力をフルパワー時の60%程度に抑える | さらに2つのコアが休止、1つが50%負荷の状態では、全体の消費電力を半分以下まで下げられる。マルチコア化してゆくCPUでは、重要な技術といえよう | |

| DICEの概念図 | ||

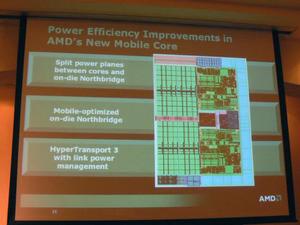

消費電力あたりの効率改善は、ノート向けCPUでは一層重要な要素である。次世代のノート向けデュアルCPUでは、HyperTransport 3リンクやメモリーコントローラーなどI/O側がCPUコア側の負荷をモニターできるようになる。そしてCPUコアがフルスピードで動作しているときはI/O側もフルスピードで動作し、2つのCPUコアがアイドル状態にある場合は、I/O側への電力供給を抑制する。これによって2倍の電力効率を実現できるとしている。

|

|---|

| 次世代のノート向けCPUコアのダイ写真。電力面ではCPUコアとI/O部が分割されているという |