|

|---|

| 4CPUコアに4GPUを搭載するハイエンドゲーマー向けプラットフォーム“4x4”の構成図。PS3が10台くらい買えそうなシステムだ |

ハイエンドのデスクトップ向けプラットフォーム技術としては、“4x4”(フォーバイフォー)と称する技術が紹介された。これはAthlon 64 FXシリーズがターゲットとしているハイエンドゲーマーなどに向けたプラットフォームへの実装を念頭に置いた技術である。デュアルコアCPU(将来はクアッドコアCPU)をデュアルプロセッサー構成で搭載したうえ、1枚のグラフィックスカード上に2つのグラフィックスチップ(GPU)を搭載したカードを、さらにデュアル構成で搭載するシステムというもの。4CPUコアと4GPUで4×4というわけだ。最初から4×4の構成でなくとも、後からグラフィックスカードを足すといった構成も可能という。ハイエンドゲーマーにとってのマルチコアシステムの価値についてヘスター氏は、マルチコアCPUを搭載するXbox 360やプレイステーション3の登場によって、ゲームのマルチコア/マルチスレッド対応は今後一層進むと述べて、パソコンゲームも同様に進化するとの見解を示した。

|

| |

|---|---|---|

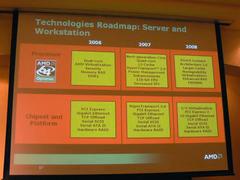

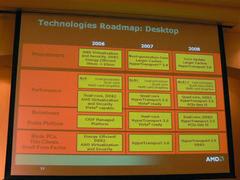

| AMDのサーバー向けCPUのテクノロジー・ロードマップ。2007年には次世代のクアッドコアCPU、HyperTransport 3リンクなどが導入される | デスクトップ向けCPUのテクノロジー・ロードマップ。2006年には仮想化技術に加えてセキュリティー技術も導入される。2007年にはハイエンド向けではクアッドコアCPUが導入される |

|

|---|

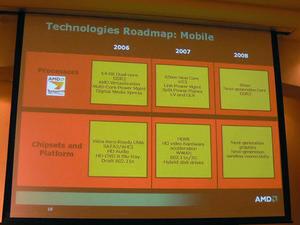

| ノート向けCPUのテクノロジー・ロードマップ。デュアルコアCPUはTurion 64 X2で導入された。2007年にはCPU内I/Oの電力制御技術が、2008年には45nm製造プロセスの導入やDDR3メモリー対応などが予定されている |

Torrenzaでは特定用途プロセッサー向けに新スロット“HTX”を提案

今回の説明会で最も注目を集めたのは、CPUとは別に特定用途向けのアクセラレーターを搭載することで、さらなるパフォーマンス向上を実現する技術“Torrenza”の紹介であった。

|

|---|

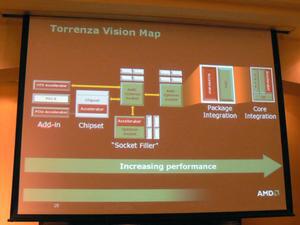

| Torrenzaによるアクセラレーターの実装方法。CPU外部に搭載する(拡張カード、専用ソケット、チップセット内蔵)方式のほかに、CPUパッケージ内に別ダイで実装する方式や、CPU内に一体化してしまう方式もあり得るという |

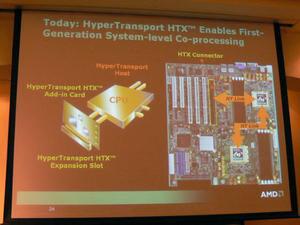

Torrenzaは米AGEIA Technologies社が開発した物理演算用プロセッサー“AGEIA PhysXプロセッサー”のように、特定用途の高速処理を行なうプロセッサー(アクセラレーター)を、CPUに直結する形で接続することで、CPUとアクセラレーターによるパフォーマンス向上を実現しようという技術だ。用途としては物理演算やグラフィックス処理で多用されるベクトル浮動小数点演算のほかに、ストリーミングメディアの処理、JavaやXMLの実行などが挙げられている。現在AGEIA PhysXはPCI Expressを利用して接続されているが、TorrenzaではアクセラレーターをHTリンク経由でCPUと直結する構成やチップセットに内蔵する構成、さらにCPUと同じパッケージに内蔵してしまう構成や、CPUコア内に実装してしまう構成など、さまざまな構成があり得るという。さらにHTリンクで接続する構成向けには、“HyperTransport HTX Expansion Slot”(HTX)という拡張カード用スロットも提案されている。

|

|---|

| HTXスロットの概念図とマザーボード上への実装例。AGPがチップセット経由でCPUとほぼ直結されたように、HTX拡張カードはHTリンクでCPUと直結される |

Torrenzaのコンセプトは、浮動小数点演算機能が別プロセッサーで提供されていた1990年代初期までのCPUを思い起こさせる。実装方法も拡張カードや専用ソケットだけでなく、CPUパッケージ内やCPU内実装など、“外付け”だけでなくCPUと一体化した方式も提案されているのが興味深い。あるいはアクセラレーター内蔵型マルチコアCPUの場合、CPUコアを増やすかわりに、Cellプロセッサーのようにアクセラレーターを増やすという方法もあり得るだろう。しかし質疑応答でも質問されたが、確実にコスト上昇につながる外付けソリューションに、どの程度市場性があるのかは疑問に思える。またアクセラレーター部分をCPUと統合するソリューションの場合、AMD以外の企業が設計したアクセラレーターを組み込むことはあり得るのか? 統合アクセラレーターの有無やその種類によってCPUの製品バリエーションは大きく増加してしまうが、それを十分に供給できるのかといった疑問の声も聞かれた。

プレゼンテーションスライドでは“Comming soon”と記述されていたTorrenzaと対応アクセラレーターが、どのような製品で登場してくるのか。非常に楽しみな技術の登場と言えそうだ。