Taiwan Semiconductor Manufacturing Company(TSMC:台湾積体電路製造)は25日、横浜のホテルで“2001 Technology Symposium”を開催した。このシンポジウムは、半導体関連企業の技術者、管理者向けに同社の最新技術と戦略を紹介するもので、日本以外にも欧米の主要都市で開催する予定。

TSMCは半導体設計は行なうが工場を持たない、いわゆる“ファブレス”企業などから注文を受けて半導体の製造を請け負う“ファウンドリー企業”。現在2ヵ所の150mmウエハーファブと9ヵ所の200mmウエハーファブを持ち、半導体生産量はファウンドリーとして世界最大。2001年には、ファウンドリー以外の半導体メーカーすべての中でも最大の生産量(200mmウエハー換算で470万枚)となる見通しという。

シンポジウムではシャンイー・チャン(Shang-Yi Chiang,Dr.)副社長らが同社の技術と戦略について説明した。

|

|---|

| Dr. Shang-Yi Chiang TSMC研究開発部 副社長 |

第4四半期には300mmウエハー工場から製品を出荷

それによると2000年第4四半期から、2社に対して0.13μmプロセスによるプロセッサーの製造を開始したが、その後も順調に立ち上がり、6月までに12の製品を出荷する予定という。歩留まりも非常によく、4MbitのSRAM(6トランジスター構成)をロット平均の歩留まりが92%であることも紹介した。

TSMCは2001年中に2つの工場で0.13μmプロセス技術の製造を開始し、2002年にはさらに300mmウエハー工場を含む5つの工場で生産を開始したいという。ただし、顧客からの要求が低ければこれを下回る可能性もあるとしている。

|

|---|

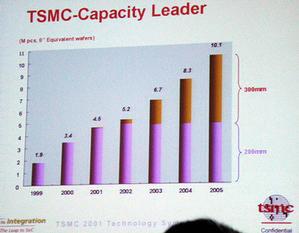

| TSMCの200mmウエハーと300mmウエハーの生産計画(200mmウエハーに換算して比較したグラフ)。2005年には1対1になるという |

300mmウエハーでの製造については、技術検証のためのパイロットラインにおいて、2月に300mmウエハーを使い0.18μmプロセスでFPGA(Field Programmable Gate Array)を製造したほか、0.13μmプロセス、銅配線技術を使ったチップを製造し、それが完全に動作することを確認したという。まず、300mmウエハーを毎月2万5000枚処理できる工場“Fab12”を建設中で、2001年第4四半期には製品の出荷をスタートする。また毎月3万枚を処理できる“Fab14”は、2002年第1四半期に製品出荷を可能にするとしている。2005年には200mmウエハーと300mmウエハーの生産量を1対1にまで引き上げる計画も明らかにした。

|

|---|

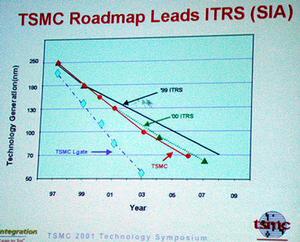

| 各国の半導体工業会が作成する国際半導体技術ロードマップ(ITRS)とTSMCの、ゲート長に関する比較グラフ。ITRSの予想(緑の点線と黒の実線)よりも速いペースでTSMC(赤線)の開発が進むとしている |

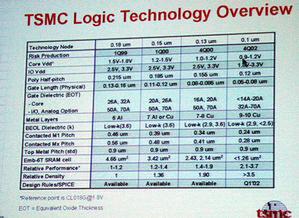

プロセス技術については、0.13μmに続いて0.10μmプロセスを開発中で、2002年第4四半期には製造が開始できる見通しで、すでに0.10μmプロセスに必要なリソグラフィー技術やマスク技術についてはめどが立ったとしている。

|

|---|

| TSMCのロジック半導体用のプロセス技術の表。2002年第4四半期には0.10μmプロセスが可能としている |

チャン副社長は「TSMCは1つ1つの技術では、世界最高レベルに達していないかもしれない。しかし、世界最高よりわずかに落ちるレベルを、半導体製造に必要なすべての技術において持っており、トータルとして世界一の製造技術を持っていると自負している」と自信を見せた。TSMCは300mmウエハー、0.10μmプロセスといった最新技術を積極的に導入し、生産量の一層の拡大を目指す構え。ただ、生産計画の数字が出るたびに断わりを入れたように、怖いのはIT市場の冷え込みによる、ファブレス企業の生産計画縮小だけのようだ。