インテル(株)は29日、報道関係者向けのテレカンファレンスにて、次世代CPU“Penryn”(ペリン)と“Nehalem”(ネハレム)についての詳細を公開した。45nmプロセスで製造されるPenrynは、2007年後半に投入の予定。

説明を担当したのは、米インテル デジタル・エンタープライズ事業部ディレクターのステファン・L・スミス氏(Stephen L.Smith)氏。スミス氏はまずPenrynの製造に使用される45nmプロセス世代のトランジスター技術について説明。45nmプロセスでは、シリコン酸化膜からハフニウムベースのHigh-Kゲート酸化膜への移行、ポリシリコンベースから金属素材のゲートへの移行など、40年ぶりとなる製造技術上の革命が盛り込まれていると述べた。そして、これらの導入により45nmプロセスで製造されるプロセッサーはよりパフォーマンスを向上させることができる。例えば、トランジスターのスイッチング速度は20%高速化され、コアの動作クロック周波数を向上させられるという。また、スイッチング時の消費電力も30%程度削減できるため、同じ熱設計の枠内でさらなるパフォーマンス向上につながる。65nmプロセスのプロセッサーと比べて、45nmプロセスでは同面積に2倍のトランジスターを集積できるため、ダイサイズを変えずに新しい機能やパフォーマンス向上を実現できるとも述べた。

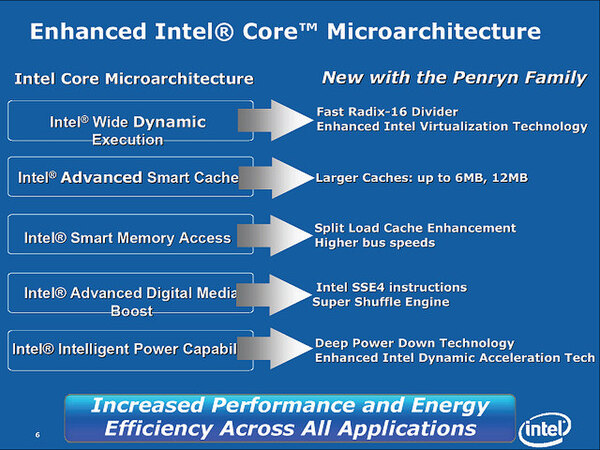

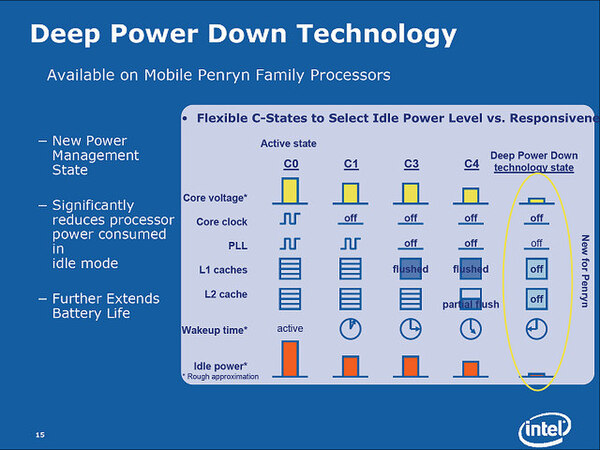

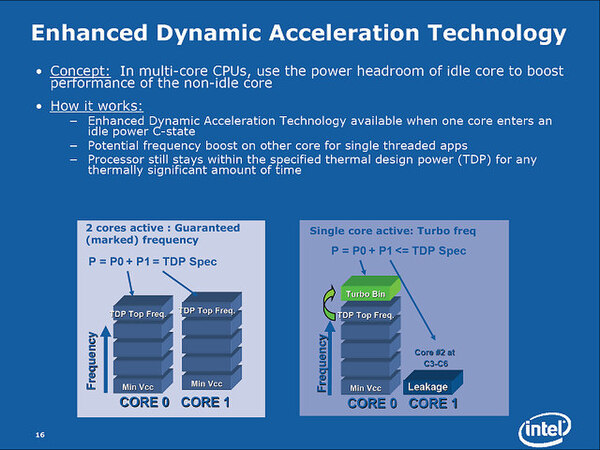

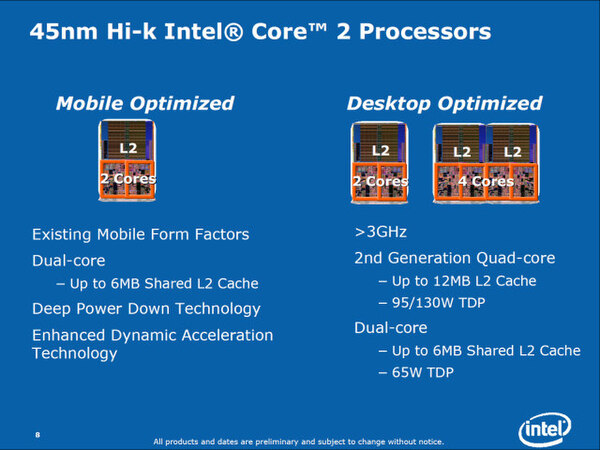

Penrynについては、現在のCoreマイクロアーキテクチャーを強化したもので、動作クロック周波数の向上によるパフォーマンス向上、新しいSSE4(Streaming SIMD Extention 4)命令の導入、内蔵2次キャッシュの増量とシステムバスの高速化などを利点として挙げている。2次キャッシュについては、デュアルコア(DC)版で6MB、クアッドコア(QC)版では12MBを搭載する。トランジスター数はDC版で4億1000万トランジスター、デュアルダイ構成のQC版では8億2000万トランジスターに達する。アーキテクチャー自体は現行Core 2 Duo(Merom)がベースであるが、コアにも機能拡張が加えられており、SSE4の追加のほか、休止中の消費電力をさらに低減する“Deep Power Down Technology”や、拡張された仮想化技術(VT)への対応、シングルスレッドのプログラムを高速化する“Enhanced Dynamic Acceleration Technology”などを実装しているという。

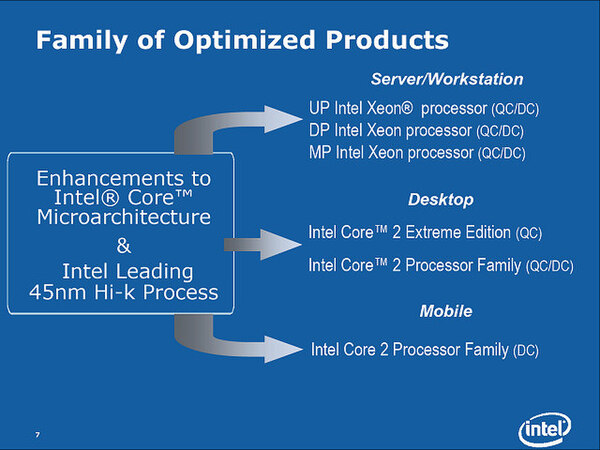

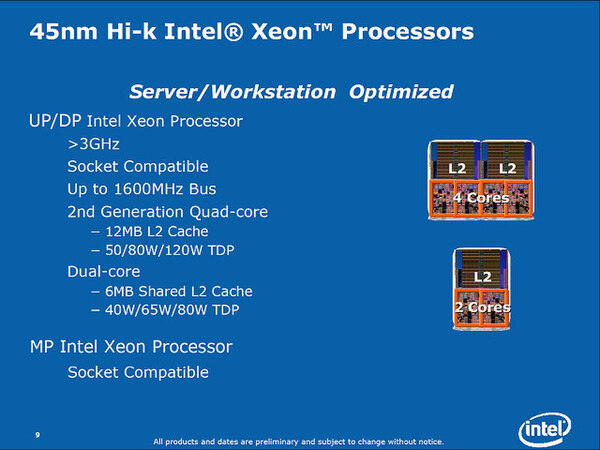

Penryn世代のCPUのラインナップは、まずXeon系列が1プロセッサーシステム(UP)、2プロセッサーシステム(DP)、4以上のプロセッサーシステム(MP)向けの全ラインで、DC版とQC版が供給される。一方デスクトップパソコン向けは、Core 2 ExtremeのラインにQC版が、それ以外のCore 2シリーズにはQC版とDC版が投入される。モバイル向けはDC版のみとなる。スミス氏は65nmプロセス版と熱設計枠は同じになると述べている。

新しいアーキテクチャーとなるNehalemは、基本的には現行のCoreマイクロアーキテクチャーの拡張版となるが、ターゲットとする市場ごとに異なる実装を選択するという。例えばシングルコアのノート向けから、8コアのサーバー向けまで幅広い製品化が可能という。CPUとチップセットを結ぶシステムバスに高速なシリアルインターコネクトを選択したり、内蔵型のメモリーコントローラーを選択することも、プロセッサーの設計上可能になる。CPUにグラフィックス機能を内蔵することも可能になるという。これによって、現在チップセットで賄っている内蔵グラフィックス機能(とメモリーコントローラー)が、CPU内に実装可能になるようだ。

もうひとつの大きな特徴が、Coreマイクロアーキテクチャーでは初めて、Hyper-Threadingのようなサイマルテニアス・マルチスレッディングの技術を取り入れる点にある。各コアが2つのスレッドを並列に動作させられる。DC版なら4スレッド、8コアのMPシステムなら16スレッドを同時実行可能となる。そのほかに、詳細は語られなかったが、マルチレベルの共有キャッシュ機能や、パフォーマンス向上に寄与する動的なパワーマネジメントなども実装されるという。

本記事はアフィリエイトプログラムによる収益を得ている場合があります