前回に引き続きIEDMで発表された論文について解説していく。今回はショートコースの中で、サムスン電子のDaehyun Moon氏による"Exploring the Evolution of DRAM Technology: Operation Principles, Scaling Challenges, and the Emergence of HBM"から、昨今のDRAMの話をしよう。

このショートコースではDRAMの基本的な構造からの説明、そしてHBMの立ち上げ時期からの変遷などを細かく説明しているが、このあたりの歴史的経緯の話は割愛させていただき、今後のDRAMの方向性、それと今後のHBMの方向性についての内容をご紹介したい。

穴を深く掘り続けるDRAMの進化、ついに物理的限界へ

DRAMは端的に言えば、穴を掘ってそこにコンデンサー(キャパシター)を構成し、このコンデンサーに電荷を貯めることで"1"を表現する(電荷が空になると"0"となる)仕組みである。

DRAMの歴史とは端的に高密度化の歴史でもあり、要するに単位面積あたりの記憶容量を増やすためには、穴の断面積を小さくすることが必須。ところが断面積を減らすと蓄えられる電荷の量が減るため、これを補うために穴の深さをどんどん増やしていった結果、最近はアスペクト比(断面積と高さの比)が1:100を超える世界になっている。

ちなみに東京タワーで1:3.5程度、東京スカイツリーでも1:9.3。世界最高層のブルジュ・ハリファでもやっぱり1:9程度になっており、いかにDRAMのアスペクト比が高いか分かろうというものである。もっともさすがにそろそろアスペクト比を高めるのも技術的に困難な領域に達しており、別の方法を考える必要がでてきている。

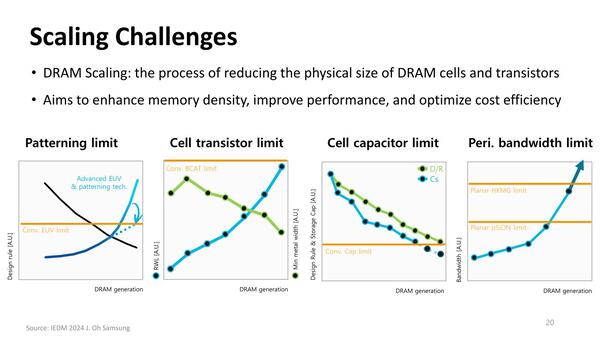

実はそのアスペクト比だけでなく、ほかにもいろいろ困難な状況になっている、というのが昨今の状況である。

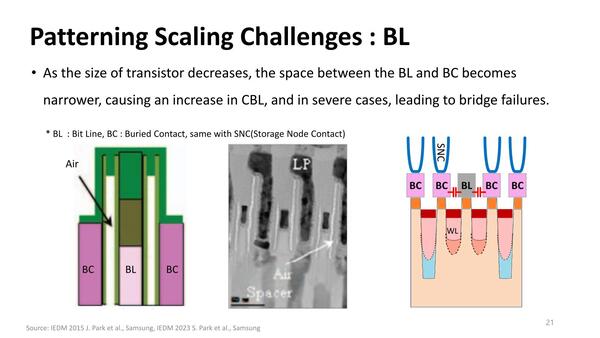

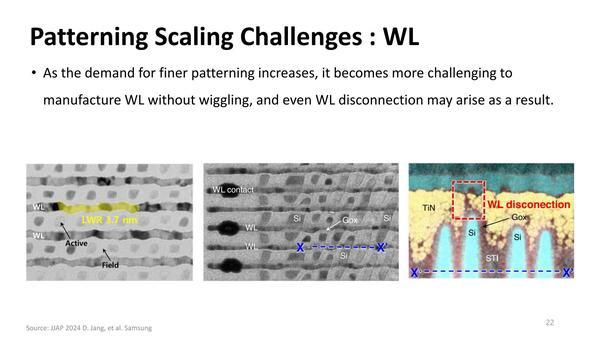

具体的に言えば、BL(Bit Line:ビット線)もセルの微細化でスペースが厳しくなっているし、WL(Word Line:ワード線)も微細化で作るのが難しくなりつつある。

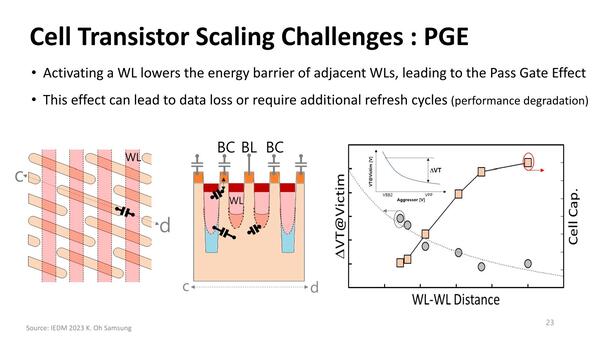

また微細化によりセル同士が隣接することに起因するPGE(Pass Gate Effect)も無視できないことになっている。対処法としてはDRAMのリフレッシュ頻度を高めることが有効だが、リフレッシュ中はDRAMのアクセスができないため性能の低下につながるし、煩雑なリフレッシュは消費電力の増大にもつながることになる。

この連載の記事

-

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 -

第854回

PC

巨大ラジエーターで熱管理! NVIDIA GB200/300搭載NVL72ラックがもたらす次世代AIインフラの全貌 -

第853回

PC

7つのカメラと高度な6DOF・Depthセンサー搭載、Meta Orionが切り開く没入感抜群の新ARスマートグラス技術 -

第852回

PC

Google最新TPU「Ironwood」は前世代比4.7倍の性能向上かつ160Wの低消費電力で圧倒的省エネを実現 - この連載の一覧へ