Intel Tech Tour 2025取材レポート

インテル復活の狼煙か!? Intel 18AプロセスのPanther Lakeの本格生産がついに始まった

2025年10月09日 22時00分更新

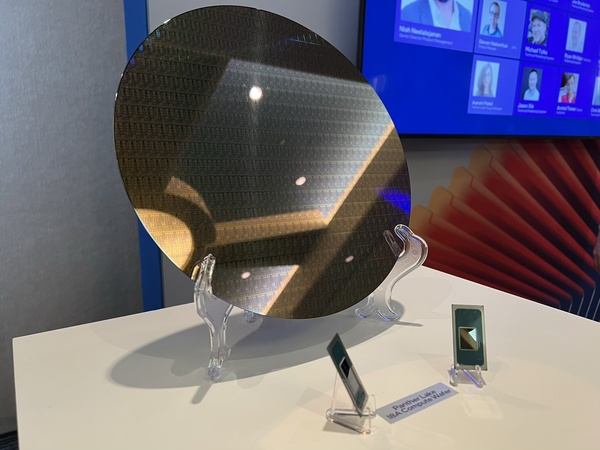

2025年10月9日22時、インテルは同社が北米アリゾナ州に建設した「Fab 52」において、同社の最新プロセス「Intel 18A」を採用した製品の多量生産に入ったことを発表した。その製品とは次世代モバイルPC&エッジAI向けCPUである「Panther Lake(開発コードネーム)」と、データセンター向けCPUである「Xeon 6+」(開発コードネーム:Clearwater Forest)である。

今回インテルが存在を明らかにした製品は2つ。1つはクライアントとエッジAI向けのPanther Lake(左)。もう1つはデータセンター向けのClearwater Forest(右)。後者は「Xeon 6+」というブランドで投入される

筆者は幸運にもインテルが主催する「Intel Tech Tour 2025」(以下、ITT2025と略)に参加できた。そこではインテルが本格稼働を始める寸前のFab 52の内部のみならず、Panther LakeならびにClearwater Forestの技術的側面まで公開された。単なる工場見学ツアーだと思っていたら、ディープな新アーキテクチャー発表イベントだったわけだ。

ともあれ、これから数回にわたって新生インテルがPanther LakeやFab 52を利用してどのような勝ち筋を模索しているのかを解説することにしよう。前もって宣言しておくが、ITT2025ではデスクトップPC向けのCPU(開発コードネーム:Nova Lake)の話は一切出てこない。モバイルPC向けCPUが主役である。

RibbonFET+PowerViaを実用化したIntel 18A

かつてインテルは半導体製造の王であり、長きにわたり半導体業界のトップを走っていた。しかし、プロセスルールが微細化するにつれ乗り越えるべき障壁が高くなり、微細化のペースが大幅にスローダウン。デスクトップPC向けCPUだと14nmプロセスをSkylakeからRocket Lakeまで使い続けることになったが、その理由は10nm移行に非常に苦労していた……という話を覚えている人も多いだろう(このあたりは大原氏の連載に山ほど良記事がある)。

デスクトップPC向けではAlder Lakeでようやく14nmプロセスから卒業したが、この時にプロセスルールの呼び方を「Intel 7」という独自呼称に変更している。Intel 7はインテルでは10nmプロセス扱いだが、近い内容のものが他社(TSMCなど)では7nmプロセスとして扱われている。ならば7nmを想起させるIntel 7と呼ぼうというわけだ。

その後、インテルはIntel 4→Intel 3と歩を進める。Intel 4を採用したMeteor Lakeでは初めてEUV(極端紫外線)露光を採用し、Intel 3への道を切り拓いた。そのIntel 3の後継が「Intel 18A」である。単位がnm(ナノメートル)からÅ(オングストローム)に変わったが、古典的な言い方をすれば1.8nmプロセスに相当する。

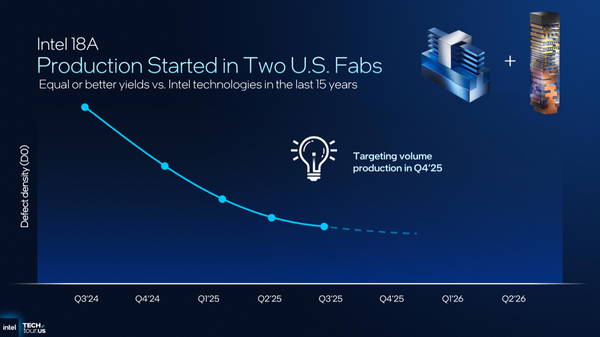

一時期は開発力低下というイメージが強かったインテルだが、Intel 18AでトップランナーであるTSMCにプロセスルールで追いつき、さらに新工場のFab 52で最新CPUの量産体制をいち早く整備。ITT2025やそれに関連する発表はインテルによる「俺は第一線に戻ってきた」という強いメッセージなのだ。

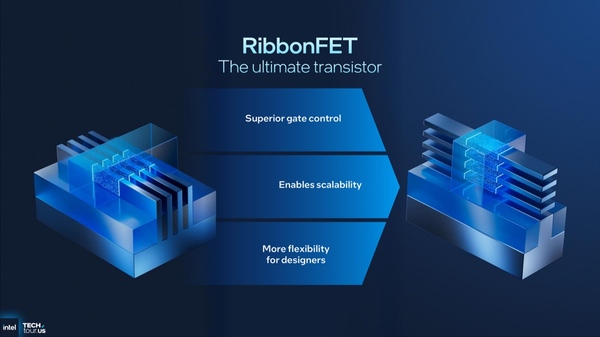

さて、肝心のIntel 18Aだが、技術的障壁をクリアーするための技術「RibbonFET」と「PowerVia」が導入されている。まずRibbonFETだが、これはすでに「GAA(Gate All Around)」技術として先行例がある。Samsungが3nmプロセスで実用化し、TSMCも次世代プロセスで採用を進めている技術である。

FinFETではトランジスターのチャネル(ソースとドレイン。論理回路ではチャネルに電流が流れ、ソースとドレインが導通すれば「1」、しなければ「0」になる)を構成する部材は薄いフィン状で成形し、垂直に立てて設置している。これに対し、RibbonFETではチャネルは非常に薄いリボン状となり、少々間隔を空けて垂直に上積みして設置する。

トランジスターのスイッチに相当するゲート(ゲートに電圧をかければチャネル間に電気が流れる)も異なる。FinFETではチャネルを上から覆うだけの構造だったが、RibbonFETではゲートの素材の中をチャネルが貫通しているという物理的な違いがある。

FinFET(左)は直立するチャネル(ソースとドレイン)の上に電極(ゲート)が覆い被さる構造。対して、RibbonFET(右)はチャネルがミルフィーユのごとく積層され、ゲートが完全にチャネルを取り囲むように配置している

RibbonFETはFinFETよりはるかに製造難度が高くなるが、FinFETよりも設計の自由度が高く、スケーリングも容易である。FinFETではトランジスターの集積度を上げようとすればそのぶんフィンを立てることになるが、フィンを増やすと水平方向に拡がっていくため、微細化には限界がある。

一方、RibbonFETはリボンを積み重ねても設置面積は変わらないため、面積的に有利である。トランジスターの特性を調整する場合においても、FinFETではフィンの数を調整するが、RibbonFETでは積層するリボンの数に加え、リボンの幅の増減も利用できるなど、設計で利用できるパラメーターが増え、結果としてより柔軟な実装が可能になる。

さらに、RibbonFETはリーク電流がFinFETより少ない。FinFETではチャネルの3方向がゲートで囲まれているが、ゲートに囲まれていない側からいくばくかの電流が逃げて(リークして)しまう。だが、RibbonFETではチャネルが完全にゲートに囲まれているため、電流のリークを大幅に抑えられる。つまり、トランジスターのゲートを完全にコントロールできるので、より高密度な実装、より高効率なチップ設計を可能にするとインテルは見込んでいる。

もう1つの柱はPowerViaだ。半導体の微細化の難しさは、トランジスターの作り込みだけではなく、トランジスター間の配線にもある。一般的に半導体はトランジスター層を最初に作り、その上に必要な配線を積み上げることで製品に仕上げていくが、電源用の配線と信号用の配線の配置が問題になる。信号用の配線は細くてもよいが、ある程度離さないとノイズの影響を受けてしまう。一方で、電源用の配線はある程度太くする必要がある。半導体の設計が微細化し複雑化するほど、両者を干渉なく共存させることは難しくなる。

そこで登場する技術がBSPDN(Backside Power Delivery Network)である。電源用の配線層(便宜的に「電源層」と呼ぶ)をトランジスター層の裏に配置すれば、配線密度が緩和され、設計難度が下がるというわけだ。表側の信号層(信号用の配線のみになった層)から見れば、太い電源用配線が消えた結果、配線に余裕が生まれる。つまり、配線同士のノイズ対策もラクになり、性能も引き上げやすくなる。

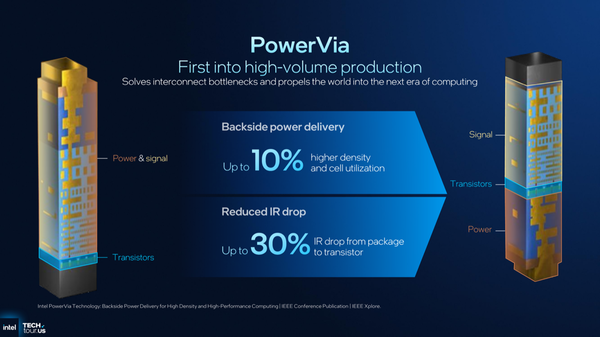

裏側の電源層から見れば、信号線を避けるような配線(得てして抵抗が高くなる)を回避できるうえに、トランジスター層に最適な配線で電力を届けられるようになる。インテルはPowerViaの採用によって配線密度が最大10%向上、トランジスターへの電圧損失が最大30%改善すると主張している。SamsungやTSMC等もBSPDN技術を今後導入予定だが、インテルはPowerViaをIntel 18Aに採り入れ、大量生産に入ったという点で一歩先んじているといえる(とはいえ、18A搭載の製品が市場に出回るのはまだ先だが……)。

従来式の配線(左)とPowerVia(右)。PowerViaではトランジスター層の裏側に電源層を配置。電力をパッケージからトランジスターまで供給するラインにおいて、電源の配線を裏に回すだけでIRドロップ(電圧降下)が30%改善するという

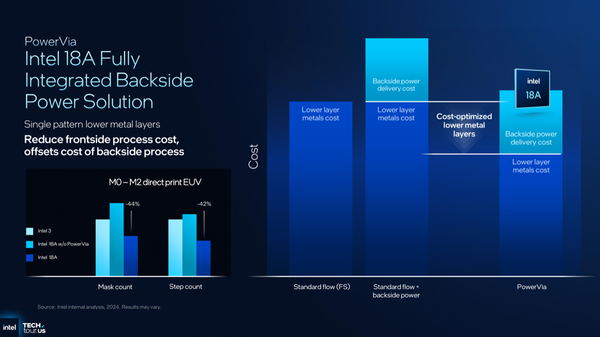

さらに、PowerViaは製造コストを下げられるという直感に反する話も飛び出した。従来通りの技法でトランジスター層と信号層を作り、裏側に電源層を作り込むというプロセスならば、裏側の作業ぶんだけコストはかさむはずだ。しかし、表側(信号層)と裏側(電源層)のプロセスを効率良く組み合わせることで、工程とマスクの数を40%以上減らすことに成功しているという。

PowerViaを利用することで信号層の配線コストを圧縮できるというグラフ(右側)と、M0〜M2層(トランジスター層に近い層)のマスク&ステップ数が40%以上削減できるというグラフ(左側)。特に後者のグラフはIntel 3よりもIntel 18A+PowerVia使用時のほうがマスク&ステップ数が少ないという点もおもしろい

RibbonFETとPowerViaの採用によってパフォーマンスも向上する。Intel 3と比較すると、ワットパフォーマンスにおいて15%以上増加、同パフォーマンスであれば25%以上の消費電力の低減。同クロックであれば、30%以上小さく作れるという。

Intel 18AはRibbonFET+PowerViaの採用でIntel 3より性能が向上。この2つのグラフはイメージ図のレベルだが、左のクロック−電力グラフはわかりやすい。ある電力(縦軸)のラインで横に線を引くと、Intel 18AのクロックはIntel 3よりも高クロック動作になる、と読める(ただし、横軸が示されていないので倍率は見てはいけない)

この最先端の技術を詰め込んだIntel 18Aプロセスを使用した製品を大量生産するための工場が、今回アリゾナで完成したFab 52というわけだ。Intel 18Aはオレゴンの工場で開発してきたが、今後アリゾナとオレゴンの工場で量産体勢に入る。インテルのファウンドリー事業はともかく、このIntel 18Aが遅滞なく量産されることが半導体業界におけるインテルに対する信頼回復の大きな指標であることは間違いない。