すでに提供されている着脱可能なファイバーカプラーを使用できる

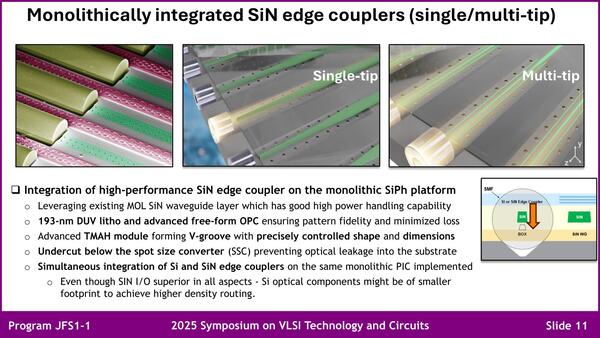

PICと光ファイバーの接続部の拡大図が下の画像である。要するにこの接続部もPIC構築時にまとめて構築できるので構築が容易、という話である。

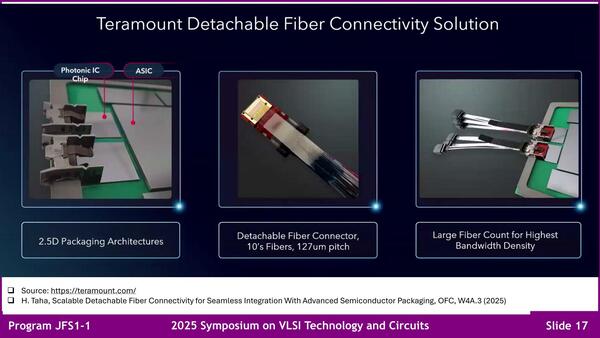

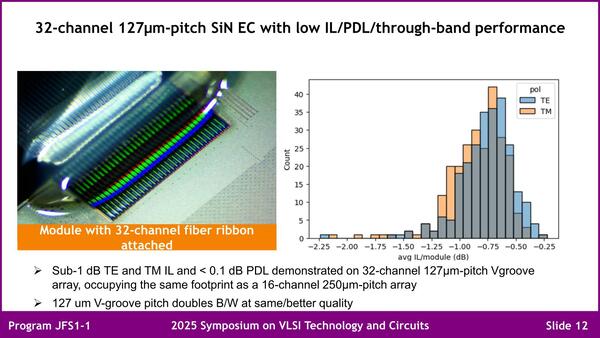

実際にこれを利用して、32本のファイバーを集積した例が下の画像である。127μmピッチで32chなので全体の幅は4mmほど。仮にファイバー1本あたり100Gbpsを流したとして、3.2Tbps/4mm=0.8Tbps/mmとなり、2022年の目標にかなり近いところまでは来ているわけだ。

ちなみに普通は送受信で別々の光ファイバーを使うことになるが、例えば送信と受信を別々の波長にして1本のファイバーで通信することも可能だし、そもそもWDMでファイバー1本あたり8波長多重にすれば、送受信を別のファイバーにしても3.2Tbps/mmが実現できるので、このあたりはいくらでもやりようがある

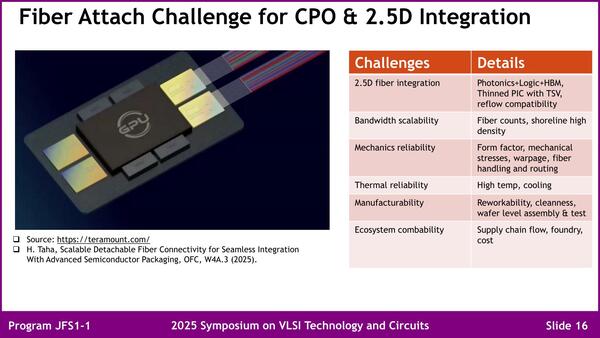

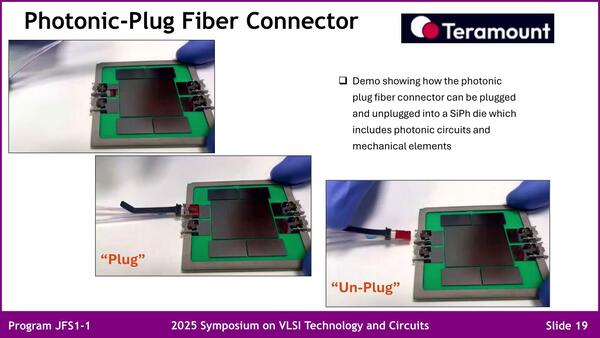

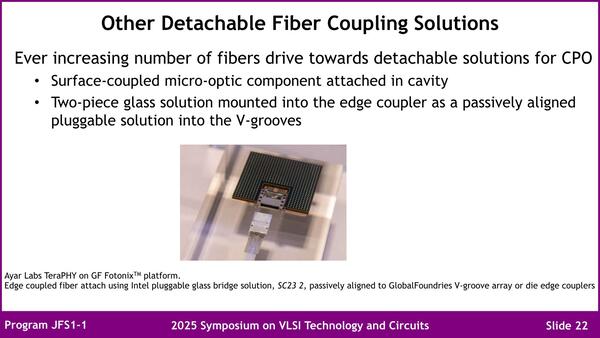

このFiber Attachを利用した、Detachable(つまり着脱可能)なファイバーのソリューションをすでに提供しているのがイスラエルのTeramountで、すでにこのGFのFiber AttachをベースにしたUniversal Photonic Couplerその他を提供している。

もちろん、必ずしもこれを使わなければいけないというものではなく、例えばBroadcomは独自のFAU(Fiber Array Unit)を提供しているわけだが、要は自社開発しなくても、すでにソリューションとして存在しているのがポイントである。実際、ASICを模したチップへのPlug/Unplugのデモも行なわれている。

他にもAyar LabsがやはりDetachable Fiber Couplerをすでにデモしており、複数のソリューションから選ぶことが可能というのも、採用を検討している企業にはうれしい部分だろう。

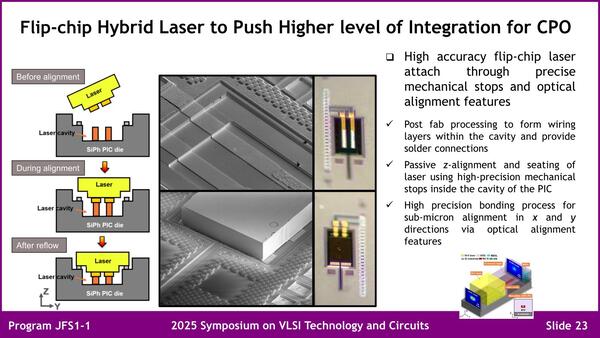

最後にレーザーソースの統合の話だ。先にも少し書いたが、Fotonixではレーザー光源は外部から入力する形になっている。その統合方法が下の画像で、ダイを構成したあとのリフロー(はんだ付け)プロセスで精度を確保して統合できるとしている。

全体としては、すでにFotonixでは確実性の高い方法で設計や製造がすでに可能になっていることを強く印象付ける講演となった。すでに第2世代、つまり45nm RF SOI CMOSプロセスに移行しているということで、このあたりはTSMCの65nm SOIよりもやや進んでいる。

その一方で、EICの方は自社で作れない(12LPPでも32Gbpsはギリギリというか少し手に余るだろう)ので、これはTSMCあたりに委託しなければいけないのが同社のウィークポイントになっている。このあたりを今後どう舵取りしていくのかが気になる部分だ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ