ビットエラーレートを少なくすると消費電力が増える問題

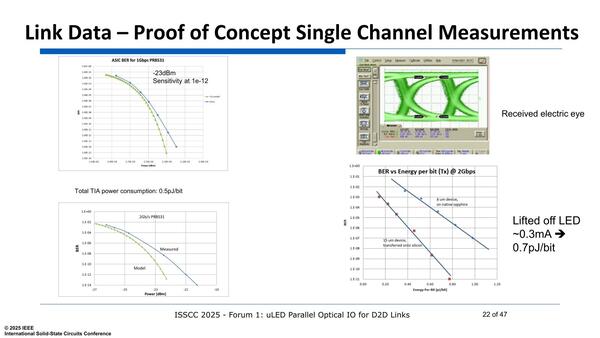

現時点ではまだ消費電力とBERがバーターになっていることが、下の画像の右下のグラフからも見て取れる。BERが10E-3と無茶苦茶多くても許容できるのであれば、消費電力は0.2pJ/bitを下回るほどに小さい。逆にBERを10E-11程度まで確保しようとすると、ほぼ0.8pJ/bit程度まで消費電力が増えてしまう格好だ。

このあたりは発光素子の構成にも関係しており、下の画像では2種類の寸法のものを比較している。やや消費電力が多いのはサファイア基板上に構築した寸法8μmのもの、低いのはシリコン基板上に構築した寸法15μmのもので、寸法を大きくすると比較的BERが下げやすい傾向が見て取れる。

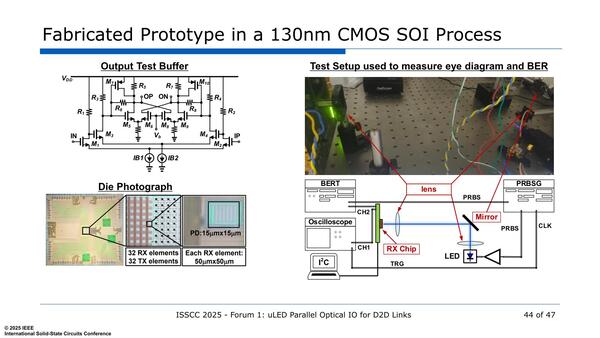

下の画像は実際の試作した送受信部であるが、PD(Photo Detector)そのものは15μm角、そのPDを含む1ch分の受光部全体は50μm角になっている。

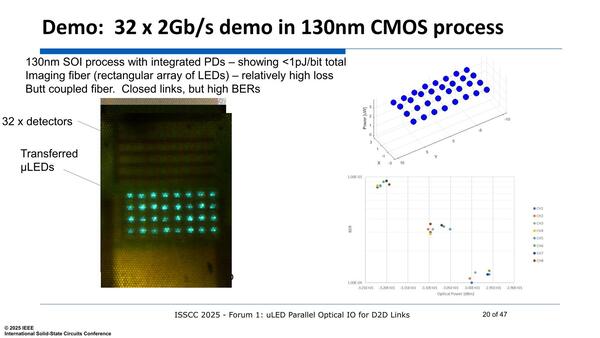

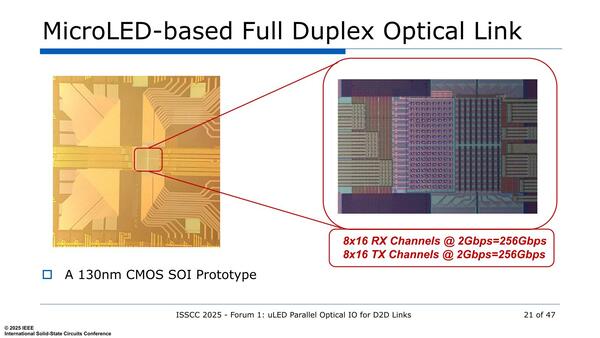

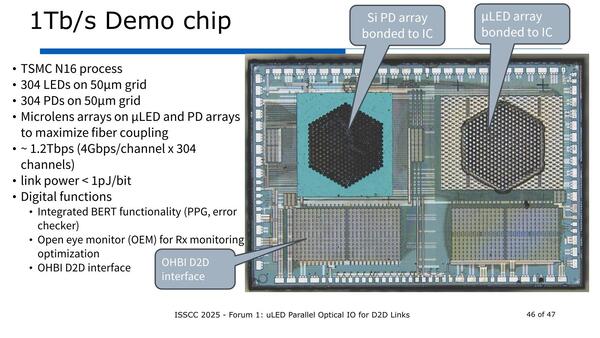

さて上3つの画像は8×4で32ch構成だが、他にも128ch構成や304ch構成の試作もされており、こちらではトータルで256Gbpsや1.2Tbpsの通信が可能になっている。

この1.2TbpsのものはOHBI(Open High Bandwidth Interconnect)という、OCP(Open Compute Project:Metaが主導を取って結成されている、サーバーの規格などを定める標準団体)に提案されたI/Fであまり一般的とは言えないのだが、あくまで研究用と考えればそれほどおかしくないし、今後他のI/Fに切り替えるのも容易だろう。

そもそも上の画像のものはTSMCのN16プロセスだから、既存のロジックCMOS用プロセスで製造されているわけで、例えばSOICを使って既存のSoCのダイの上に、直接このMicroLEDの送受信ダイを3次元積層するなんてことも技術的には可能であろう。このあたりはこの先なんとでもなる話であり、将来的にはロジックダイに直接これを仕込むことも十分可能だろう(その場合、今度は2つのチップレットの間の光の送受信の経路をどう構築するかという問題が出てくる)。

論文ではさらに、それほど回路を複雑化させずにBERを引き下げるための方法論や送信/受信の回路構成の提案などをしているが、さすがにこのあたりは細かい話になるので割愛する。ただ、従来の光イーサネットなどに使われる技法に比べるとかなりシンプルなもので、消費電力やレイテンシーが無駄に増えることもなさそうな見通しである。

あくまでも将来技術の1つの候補でしかないのだが、Die-to-Dieの光接続の可能性を見せてくれる話であった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 - この連載の一覧へ