ロードマップでわかる!当世プロセッサー事情 第797回

わずか2年で完成させた韓国FuriosaAIのAIアクセラレーターRNGD Hot Chips 2024で注目を浴びたオモシロCPU

2024年11月11日 12時00分更新

テンソル縮約に特化した内部構造

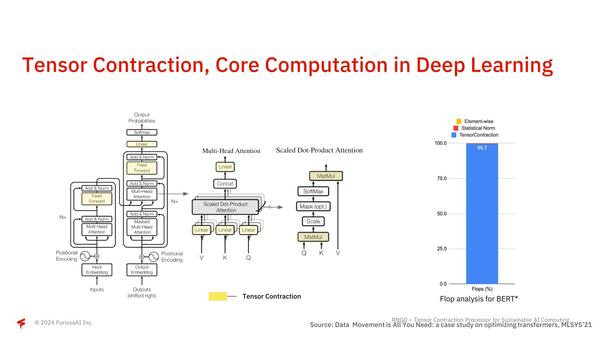

さて第1世代のWarboyでは公開されなかったNPUの中身である。RNGDではTCP(Tensor Contraction Processor)と呼んでいるが、そもそも畳み込みニューラルネットワークなどでは計算の大半がテンソル縮約(Tensor Contraction)の計算に費やされている。

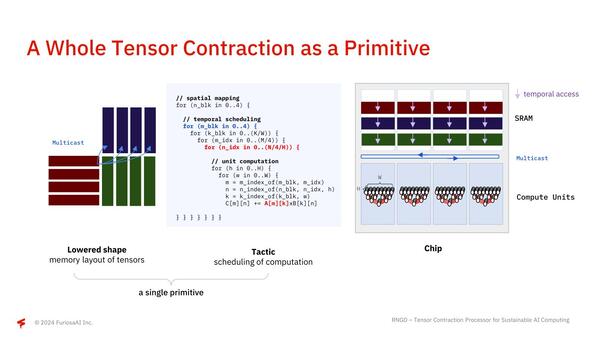

このテンソル縮約は要するに行列積(Matmul)であって、世の中に多く存在するテンソル演算用のアクセラレーター(例えばNVIDIAのGPUに搭載されるTensor Core)はこの行列積を高速に実行するための機構を搭載しているのだが、テンソル縮約≠行列積ではない、とFuriosaAIは主張する。

要するに扱うべき行列のサイズは、大抵の行列積演算ユニットのものよりはるかに大きいので、固定サイズの行列積演算ユニットを使うのは不効率、というわけだ。RNGDはこれをどうしたかというと、行列のサイズに合わせて行列積の計算に使うコンピュートユニットの数をダイナミックに変更しながら、目的のサイズの行列積を一発で行なえる、というところが異なるとする。

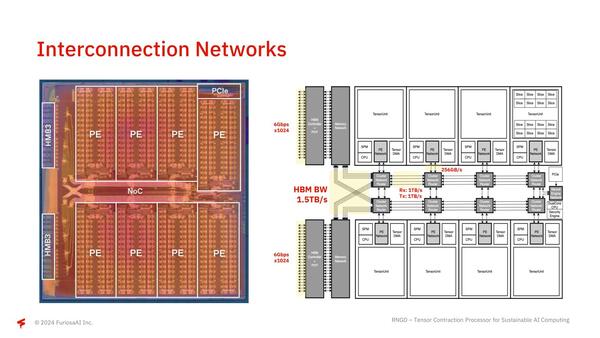

下の画像左側がそのRNGDの構成で、1個あたり64TOPS/32TFlopsの演算性能と32MBのSRAMを搭載するTensor Unitが8つ搭載されている。右側はその個々のTensor Unitの構成で、内部的には8つのプロセッサー・エレメントが配される。

ここでFetch/Commit Sequencerと、テンソル縮約を行うContraction EngineやVector Engine/Transpose Engine/Commit Engineの間にスイッチが入っているのがミソで、大規模な行列に対してすべてのContraction Engine類が協調する形で処理できるようになっている。また個々のTensor Unitの間は非常に高速なNoCでつながっており、HBM3の帯域をすべてのTensor Unitで使い切れるような構成になっている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ