ロードマップでわかる!当世プロセッサー事情 第792回

大型言語モデルに全振りしたSambaNovaのAIプロセッサーSC40L Hot Chips 2024で注目を浴びたオモシロCPU

2024年10月07日 12時00分更新

Hot Chips第5弾は、SambaNovaのSC40Lを取り上げたい。SambaNovaと同社の最初のプロセッサーであるSC10は連載595回で説明しており、今回はここからのアップデートになる。

SambaNovaのSN30。同社の紹介ビデオより。ちなみにパッケージ自体はかなり大きい

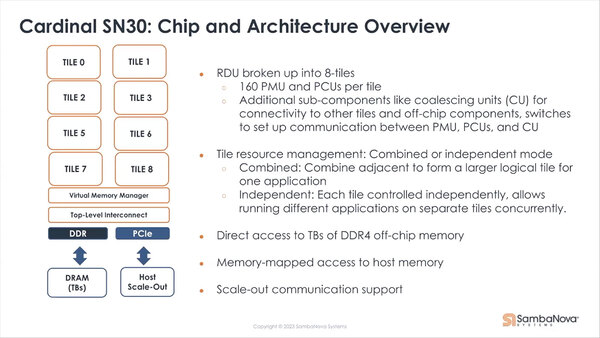

前回は2020年12月で、ちょうどCardinal SN10というチップをリリースした直後である。この後2021年、SambaNovaはCardinal SN20をリリース、そして2022年にCardinal SN30をリリースしている。ただこのSN20とSN30は同じもので、SN20×2がSN30という構成である。スペックをまとめると以下になる。

| 各プロセッサーのスペック | ||||||

|---|---|---|---|---|---|---|

| SN10 | SN20 | SN30 | ||||

| 製造プロセス | TSMC N7 | TSMC N7 | TSMC N7 | |||

| トランジスタ数 | 400億 | 430億 | 430億×2 | |||

| RDUコア数 | 640 | 640 | 640×2 | |||

| SRAM容量 | 320MB? | 320MB | 320MB×2 | |||

| Off-Chip DRAM | DDR4×6ch? | DDR5×3ch? | DDR5×4ch? | |||

| FP16性能(TFlops) | 320 | 344? | 688 | |||

要するにSN20はSN10のマイナーバージョンアップといった構成で、SRAM容量を若干増やしたのと、おそらくは動作周波数をやや引き上げた程度の差しかない(この話は後述する)。

SN20を利用した製品とサービスは存在はしたのだろうが、すぐにSN30に置き換えられることになってしまった。なぜ「存在はしたのだろう」と言えるかというと、同社の提供するSoftware Tuning ToolであるSambaTuneのRelease Notesに"Release 1.17 (2023-10-20) Added GPT13B examples for SN20 and SN30."の文言があるからである。ただ、どの程度の期間SN20を利用したサービスが提供されていたのかはやや疑わしい。

もう1つ謎なのが、DRAMの種別である。2020年にSN10が発表された時のスライドによれば、TBクラスのメモリーを外付けできるという話であった。これに関しては、Hot Chips 33のスライドで、SN10-8R(SN10を8チップ搭載したシステム)がDDR4-2677を48ch接続して容量12TBであると記述されており、つまり1個のSN10にはDDR4-2667を6ch接続でき、おのおの256MBで合計1.5TBの容量になる、と考えられる。

SN20/SN30に関してはDDR5、という話が出ている2021年4月にSamsung Electronicsが公開したTech Blogによれば、SambaNovaのプラットフォームはDDR5を利用する、と説明されている。帯域的に言えば2021年末の段階ではまだDDR5-4800がなんとか出てきた程度の段階なのでDDR4に比べて帯域が倍というわけにはいかないのだろうが、容量的にはDDR4の2倍までサポートしていることもあり、おそらくはチャネル数を半分に減らしても同程度の容量(最大1.5TB)が可能になったものと思われる。

時期的な問題を考えると、ここでDDR4を使い続けるメリットは乏しい。なのだが、これと矛盾した資料が(しかもSambaNova公式から)出てきているのが頭が痛い。下の画像はALCF(Argonne Leadership Computing Facility)に納入されたSambaNovaのSN30ベースのプラットフォームの説明なのだが、ここには"TBs of DDR4 off-chip memory"とか書かれているのがわかる。

SN30ベースのプラットフォーム。こちらはALCFの動画から確認できる。この図で言うところの"Top-Level Interconnect"がまた肝だったりする

この"off-chip"がまた意味深だったりするのだが、それはともかくとして2022年にリリースされた製品がDDR4というのは正直考えにくい。ここはおそらくDDR5のタイプミスだと筆者は考えている。したがって、先の表は"DDR5?"としたわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ