前回の記事を書いていて思い出したのがQuarkである。これに振り回された人はご愁傷様としか言いようがない考えなしのプロセッサーであり、しかもずるずると引きずった挙句に突然消えるという、猛烈にはた迷惑な製品であった。ということで、若干ながら振り回された側という恨みも込めて、久々のCPU黒歴史シリーズである。

超小型・低消費電力を武器に

IoT市場に対してインテルが売り込む

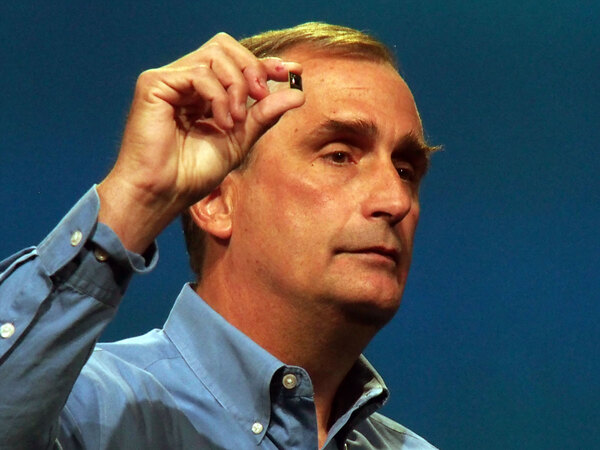

2013年9月にサンフランシスコで開催されたIDF Fall 2013の初日基調講演において、当時のCEOだったBrian Krzanich氏が突然発表したのがQuarkとEdisonである。ジサトライッペイ氏の当時のIDFレポートにも少し出ている。

もっともEdisonに関しては、正式に発表されたのは翌2014年1月のCES、その詳細が公開されたのは2014年のIDFのことである。

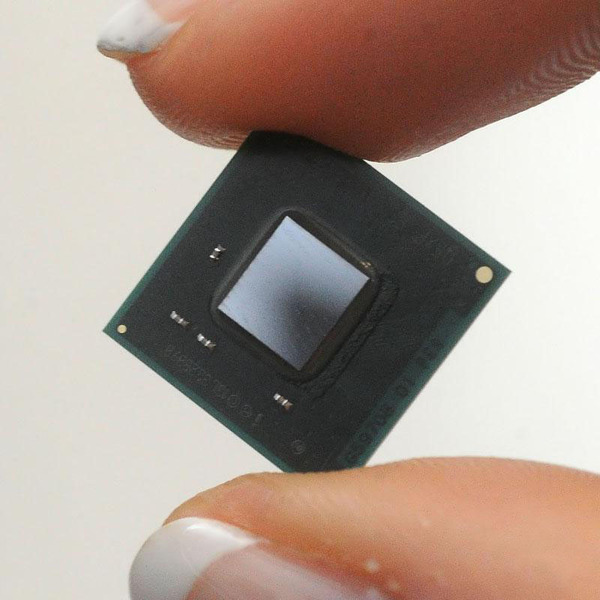

順序が逆になるが、Edisonから説明しよう。Edisonは超小型のコンピュート・モジュールである。先のイッペイ氏の記事にもあるが、Silvermontベースの2コア Atom(500MHz駆動)に1GB LPDDR3と4GB eMMCフラッシュ、Wi-FiとBluetoothを搭載するモジュールで、寸法は35.5×25×3.9mmと非常に小さい。

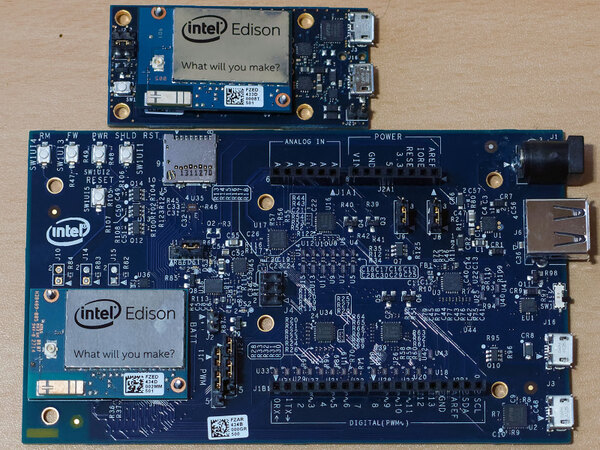

裏面(写真右側)に70ピンの拡張コネクターがあり、ここ経由でSDカードやUART、I2/SPI、USB 2.0、GPIOなどの配線を引っ張り出せる(電源供給もこの端子から)。表面(写真左側)は、Wi-Fi/Bluetoothのアンテナ端子があるだけだ

内部構造は下の画像のとおりで、余分なものが一切搭載されていない。そのため、この状態で使うのはかなり困難である。それもあってインテルからはEdison用の開発キットも提供されていた。

上側は本当に最小限のボードで、USBコネクターとリセットスイッチ以外はなにもないのだが、70ピンのコネクターからの信号をピンヘッダに変換できるようになっており、機器に実際に組み込むことを前提にしたものだ。

一方下側はArduino互換のI/Oピンなどを搭載し、製品への組み込みと言うよりもその前段階の評価や試作などを目的としたものである。

ところで搭載されているのは500MHzながらAtomであり、メモリーも1GB搭載していることもあり、ここでは普通にLinuxが稼働する。それもあって、比較的組み込み用途に利用しやすいと考えたようだ。実際に利用されたか? というのはまた別の話であるが。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ